# **University Of Natal**

# A Network based Rapid Prototyping System for Applications in Research and Engineering Education

Ву

# **Magash Pillay**

Submitted in partial fulfilment of the academic requirements for the degree of Master of Science in Engineering, in the Department of Electrical Engineering, University of Natal, Durban, South Africa

February 2001

I hereby declare that all the material incorporated into this thesis is my own original and unaided work except where specific reference is made by name or in the form of a numbered reference. The work contained herein has not been submitted for a degree at any other University.

Signed\_//

M. Pillay

Date: 03/02/2002

## **ABSTRACT**

Engineering educators the world over are being faced with the dilemma of combining traditional mathematically intensive courses, like Control Systems and Robotics with advances in computational hardware and software. This is because it is impractical to include both software engineering issues as well as conventional course content.

A solution to the problem lies in Rapid Prototyping technology to develop and design software, for application on PC's and embedded systems. Rapid Prototyping, based on automatic code generation, allows users to develop advanced software on high level graphical platforms like Simulink® and LabView®, while "hiding" the underlying layers of complex code. This approach allows the advanced hardware, traditionally reserved for software engineers, to be accessed by a much wider audience and is an ideal educational tool.

This thesis presents the complete development of the Rapid Application Development Environment (RADE). The RADE system customises the Mathworks Real Time Workshop (RTW) revision 11 for application on both standalone and networked DSP cards. The functionality of the RTW is incorporated into the RADE system. This affords the user seamless code generation, downloading, online parameter tuning and on-line data visualisation with storage capability. An added advantage of the RADE system is its easy portability to multiple target platforms, which is demonstrated by its implementation on two different DSP cards.

Finally the functionality of the RADE system is demonstrated as an educational tool, with the demonstration of a DC motor speed and position controller.

| Dedication                                                                                |  |  |

|-------------------------------------------------------------------------------------------|--|--|

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

| ,                                                                                         |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

| With deep gratitude and affection to my uncle Authemullam Govender and my anut Visalachee |  |  |

| Kuppasamy for their support and guidance.                                                 |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

|                                                                                           |  |  |

## **ACKNOWLEGMENTS**

I will like to express my greatest thanks to my supervisor Mr Gregory Diana. Who has endeavoured and succeed in establishing a stimulating and challenging environment at the Motion Control Group in the Department of Electrical Engineering at the University of Natal. His guidance and encouragement throughout this project has been sincerely appreciated.

The following people have also supported me during the course of this work

My family and friends for their understanding and support;

My colleagues Adam Stylo, Myles Walker and Cedric Worthmann for providing a friendly working environment. In addition Adam Stylo requires special mention for laying the groundwork for this project.

The academic and technical staff of the Electrical Department, who are always willing to assist students,.

| CHAPTE     | R ONE: INTRODUCTION                        | 1-1  |

|------------|--------------------------------------------|------|

| 1.1. Gene  | eral                                       | 1-1  |

| 1.2. An O  | Overview of Work Presented                 | 1-1  |

| 1.3. Thes  | is Sructure                                | 1-3  |

| 1.4. Publi | ications and Contributions                 | 1-3  |

| СНАРТЕ     | ER TWO: LITERATURE SURVEY                  |      |

| 2.1. Intro | oduction                                   | 2-1  |

| 2.2. Real  | Time Rapid Prototyping                     | 2-1  |

| 2.2.1      | The Conventional Real-Time Design          | 2-2  |

| 2.2.2      | The Rapid Prototyping Approach             | 2-3  |

| 2.2.3      | The Role of Rapid Prototyping in Education | 2-3  |

| 2.2.4      | Hypersignal                                | 2-5  |

| 2.2.5      | The Mathworks Rapid Prototyping Framework  | 2-6  |

| 2.3. Thir  | d Party Tools Based On The Mathworks RTW   | 2-7  |

| 2.3.1      | dSPACE                                     | 2-7  |

| 2.3.2      | Use of dSPACE in Engineering Education     | 2-8  |

| 2.3.3      | Complete Experimental Solutions            | 2-10 |

| 2.4. Acad  | lemic Developments with RTW                | 2-11 |

| 2.4.1      | Control System Development Environment     | 2-11 |

| 2.4.2      | Work at Other Academic Institutions        | 2-13 |

| 2.5. Cont  | text of Work Presented in this Thesis      | 2-15 |

| 2.5.1      | Categories of RTW Targets                  | 2-16 |

| 2.5.2      | Summary Of Project Goals                   | 2-17 |

| 2.6. Con   | clusion                                    | 2-18 |

| СНАРТ      | ER THREE: OVERVIEW OF SIMULINK AND THE RTW | 3-1  |

| 3.1. Intro | oduction                                   | 3.1  |

| 3.2. Prod  | ucts Available From The Mathworks           | 3-1  |

|------------|---------------------------------------------|------|

| 3.3. A Ov  | verview Of Simulink                         | 3-3  |

| 3.3.1      | An Example with Simulink                    | 3-3  |

| 3.3.2      | How Simulink Works                          | 3-7  |

| 3.3.3      | An Overview of S-functions                  | 3-8  |

| 3.4. The 1 | Real Time Workshop                          | 3-11 |

| 3.4.1      | An Overview of the RTW                      | 3-12 |

| 3.5. Targ  | et Language Compiler                        | 3-14 |

| 3.5.1      | System Target Files                         | 3-16 |

| 3.5.2      | Block Target Files                          | 3-17 |

| 3.6. The   | Code Build Cycle                            | 3-20 |

| 3.6.1      | Make Utilities                              | 3-20 |

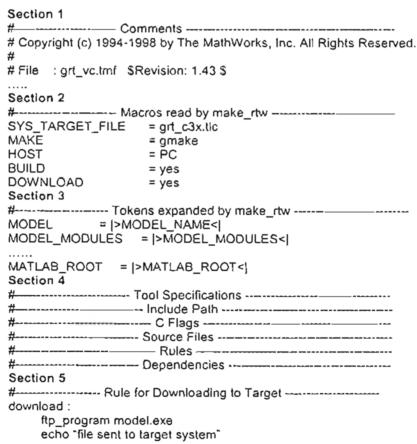

| 3.6.2      | System Template Make File                   | 3-21 |

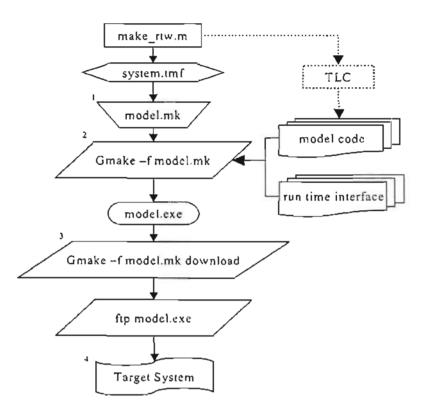

| 3.6.3      | The Build Flow Diagram                      | 3-22 |

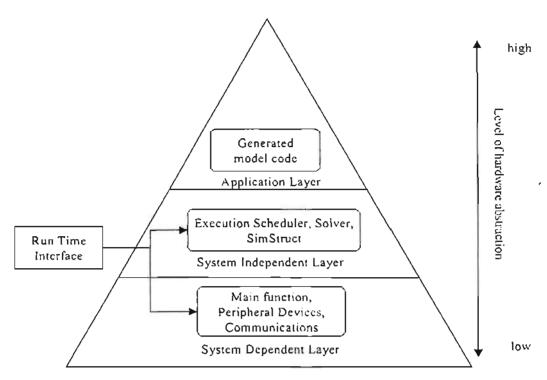

| 3.7. Rapi  | id Prototyping Program Architecture         | 3-24 |

| 3.7.1      | System Dependent Layer                      | 3-24 |

| 3.7.2      | System Independent Layer                    | 3-25 |

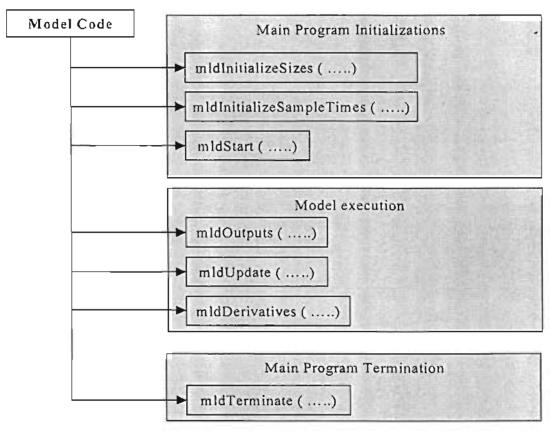

| 3.7.3      | Application Layer                           | 3-26 |

| 3.8. The   | Mathworks TCP/IP External Mode              | 3-26 |

| 3.8.1      | Message Frames Between Simulink and Target  | 3-28 |

| 3.8.2      | Simulink Internals                          | 3-29 |

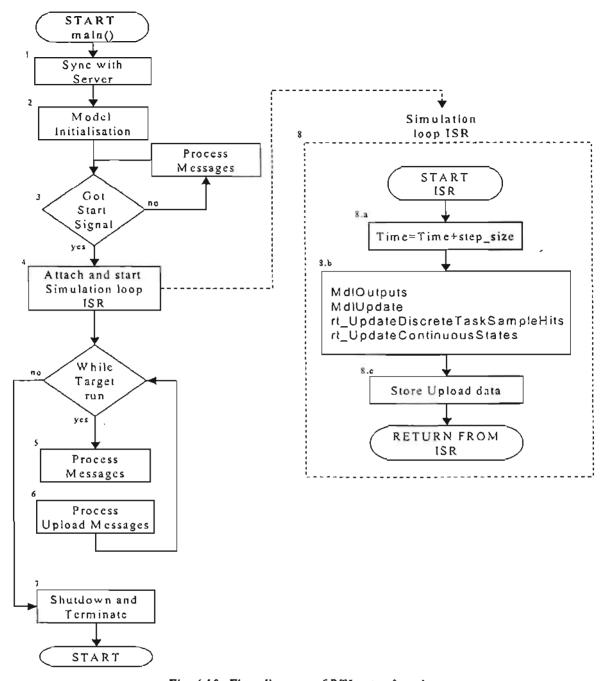

| 3.8.3      | Target Internals                            | 3-31 |

| 3.9. Con   | clusion                                     | 3-32 |

| CHAPT      | ER FOUR: DESIGN OF THE RADE FRAMEWORK       | 4-1  |

| 4.1. Intr  | oduction                                    | 4-1  |

| 4.2. Dev   | eloping the RADE framework                  | 4-1  |

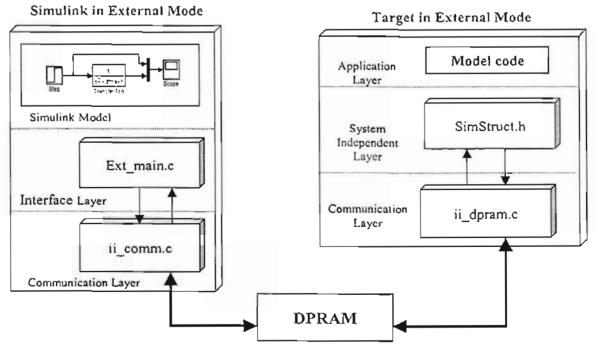

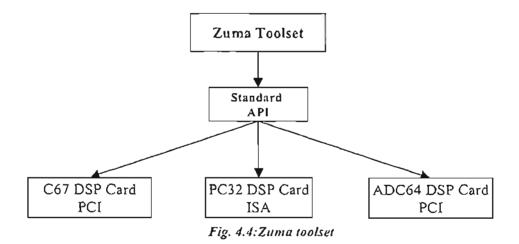

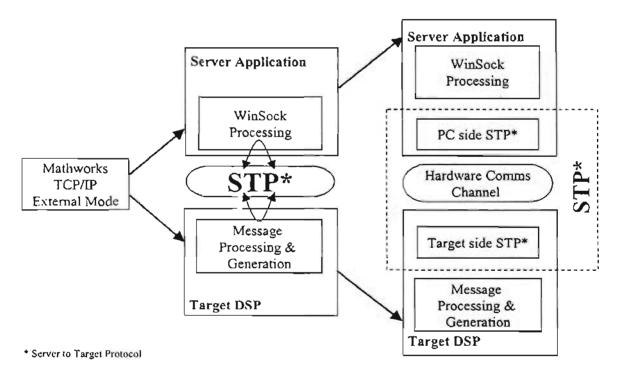

| 4.2.1      | Mathworks TCP/IP External Mode Architecture | 4-1  |

| 4.2.2      | CSDE External Mode Architecture             | 4-2  |

| 4.2.3      | RADE External Mode Architecture             | 4-3  |

| 4.3. Perip | ohera! Issues                                   | 4-5  |

|------------|-------------------------------------------------|------|

| 4.3.1      | Windows Sockets                                 | 4-5  |

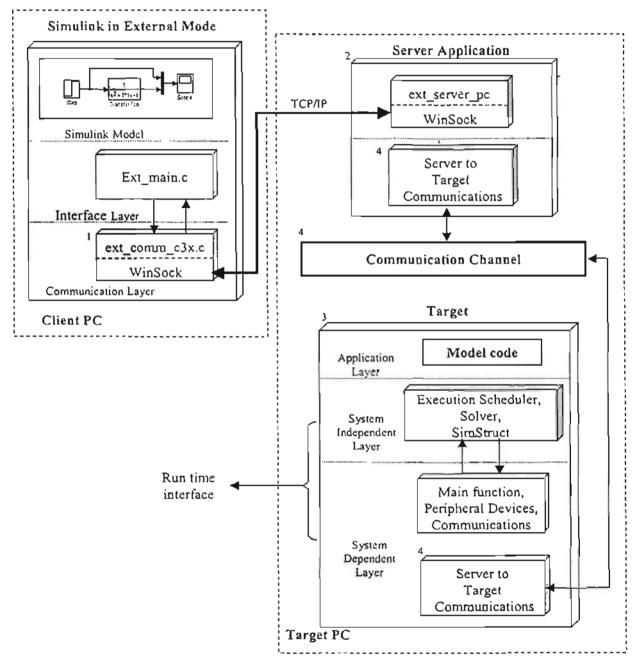

| 4.3.2      | Zuma Toolset for Target Development             | 4-6  |

| 4.4. Mod   | ifications to the Simulink Communication Layer  | 4-8  |

| 4.4.1      | Conversion Functions                            | 4-8  |

| 4.4.2      | Function Registration                           | 4-11 |

| 4.5. Serv  | er Application                                  | 4-12 |

| 4.5.1      | Graphic User Interface                          | 4-14 |

| 4.5.2      | File Transfer Process                           | 4-15 |

| 4.6. Targ  | get Run Time Interface                          | 4-16 |

| 4.6.1      | System Dependent Layer                          | 4-17 |

| 4.7. RAD   | DE Communications                               | 4-18 |

| 4.7.1      | Server to Target Protocol                       | 4-19 |

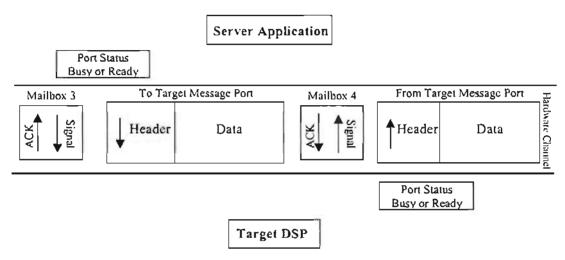

| 4.7.2      | Message Port                                    | 4-20 |

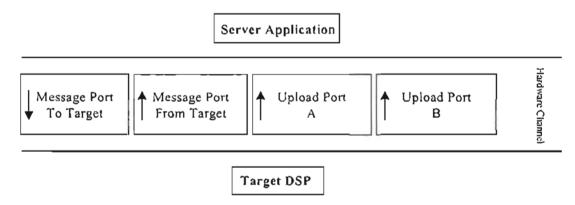

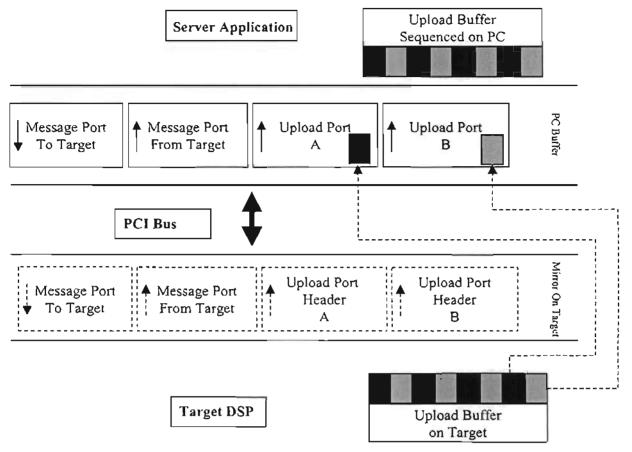

| 4.7.3      | Upload Data Port                                | 4-22 |

| 4.8. Con   | clusion                                         | 4-23 |

| CHAPTE     | ER FIVE: RADE PC32 IMPLEMENTATION               | 5-1  |

| 5.1. Intro | oduction                                        | 5-1  |

| 5.2. Desc  | eription of PC32 Card                           | 5-2  |

| 5.3. TMS   | S320C32                                         | 5-4  |

| 5.4. Desc  | cription of PWM Card                            | 5-6  |

| 5.5. Devi  | ice Drivers                                     | 5-8  |

| 5.5.1      | ADC's                                           | 5-9  |

| 5.5.2      | DAC's                                           | 5-10 |

| 5.5.3      | PWM                                             | 5-11 |

| 5.5.4      | Asynchronous Interrupt Support                  | 5-11 |

| 5.6. Cus   | tomising RADE for the PC32                      | 5-14 |

| 5.6.1      | External Mode and the Server to Target Protocol | 5-14 |

| 5.6.2      | System Target File                              | 5-17 |

| 5.6.3       | Template Make File                                    | 5-19 |

|-------------|-------------------------------------------------------|------|

| 5.7. Conc   | lusion                                                | 5-20 |

| CHAPTE      | R SIX: RADE ADC64 IMPLEMENTATION                      | 6-1  |

| 6.1. Intro  | duction                                               | 6-1  |

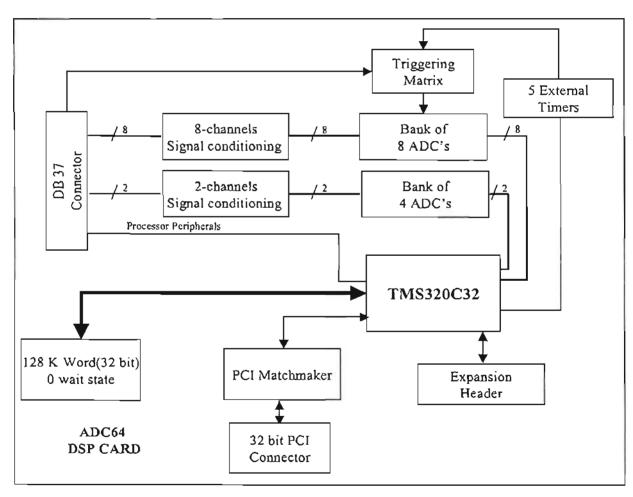

| 6.2. Desci  | ription of ADC64 Card                                 | 6-1  |

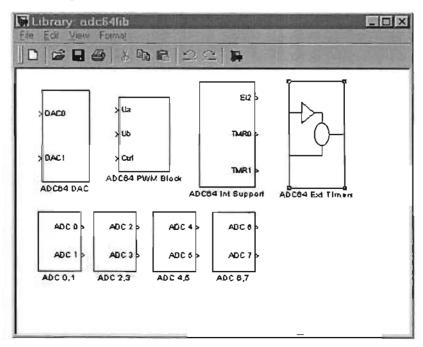

| 6.3. Device | ce Drivers for the RADE ADC64                         | 6-4  |

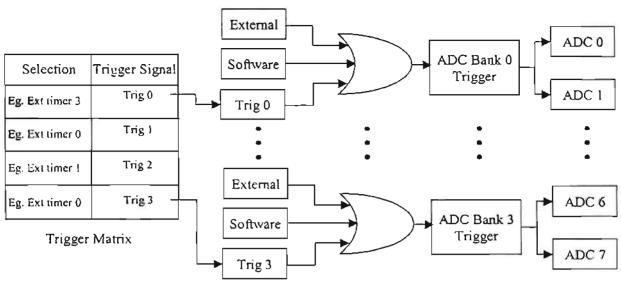

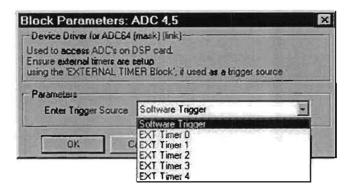

| 6.3.1       | ADC's                                                 | 6-5  |

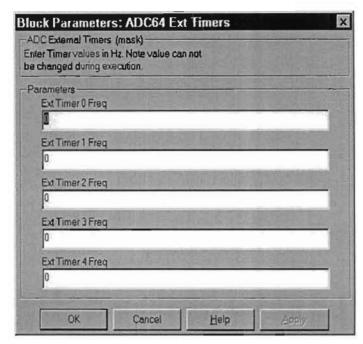

| 6.3.2       | External Timers                                       | 6-6  |

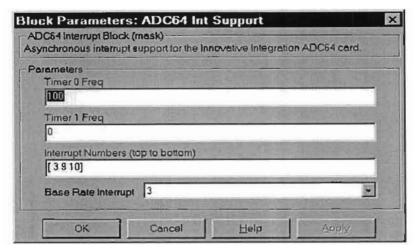

| 6.3.3       | DAC's, PWM and Interrupt Blocks                       | 6-7  |

| 6.4. Cust   | omising RADE framework for the ADC64 Card             | 6-8  |

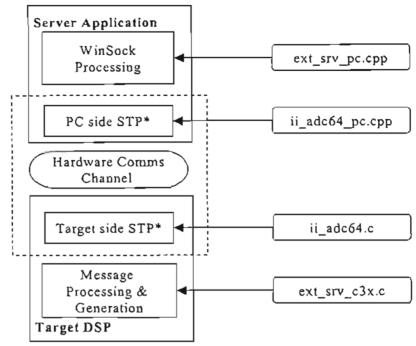

| 6.4.1       | External mode and Server To Target Protocol           | 6-8  |

| 6.5. Cond   | lusion                                                | 6-12 |

| СНАРТЕ      | R SEVEN: DEMONSTRATION OF THE RADE SYSTEM             | 7-1  |

| 7.1. Intro  | duction                                               | 7-1  |

| 7.2. A Ca   | se Study: Designing a DC Servo Motor Speed controller | 7-2  |

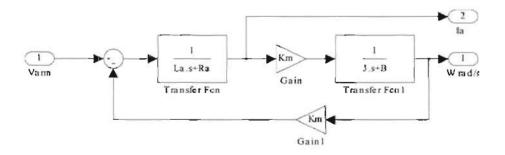

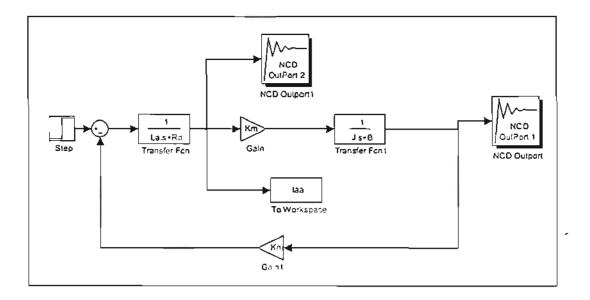

| 7.2.1       | Motor Model                                           |      |

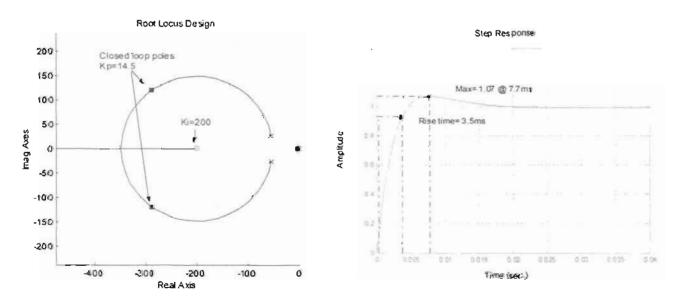

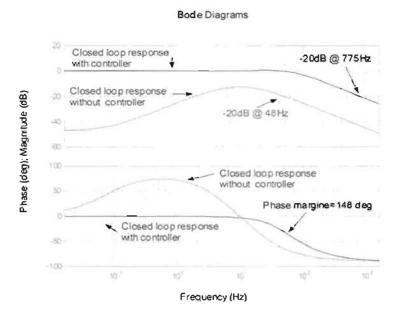

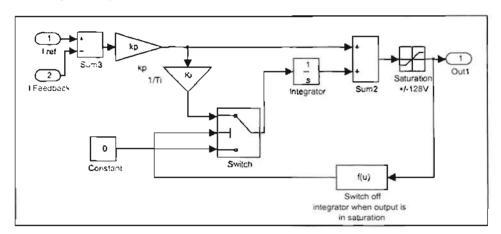

| 7.2.2       | Design of Current PI Controller                       | 7-3  |

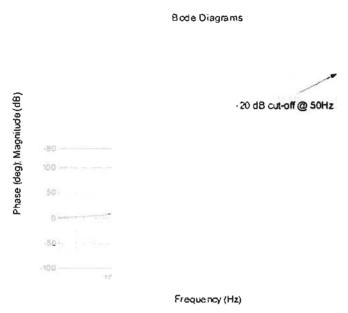

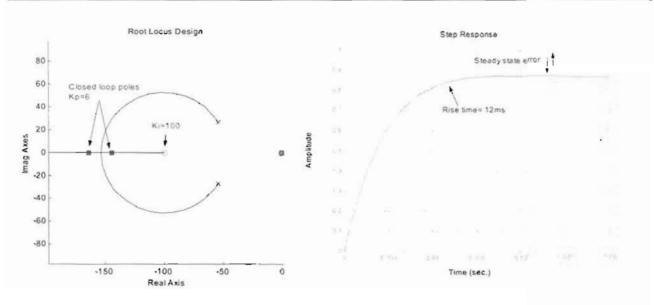

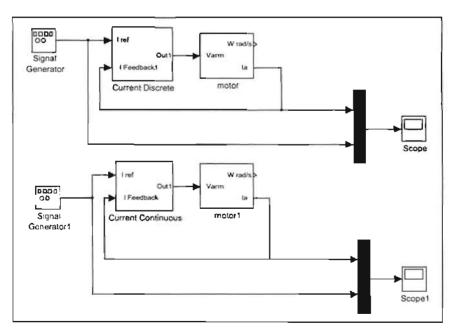

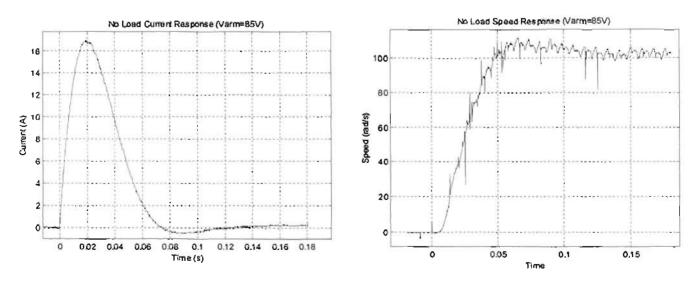

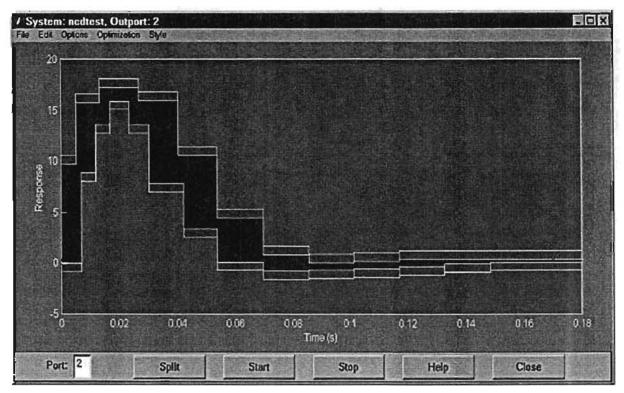

| 7.2.3       | Simulation of Current Controller                      | 7-7  |

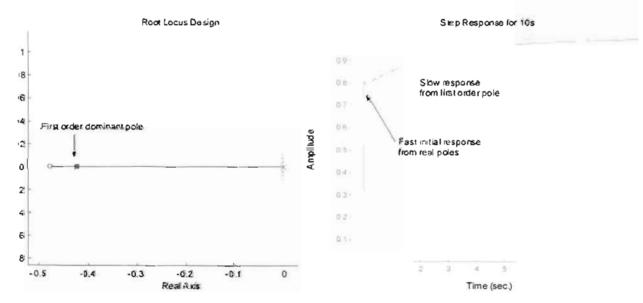

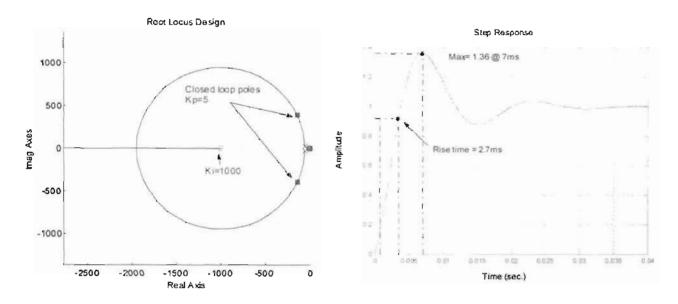

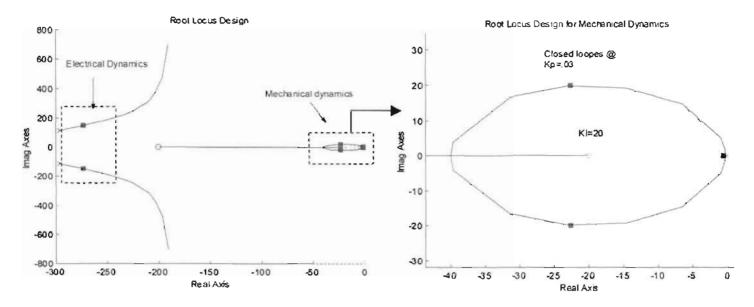

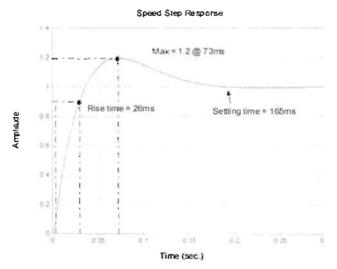

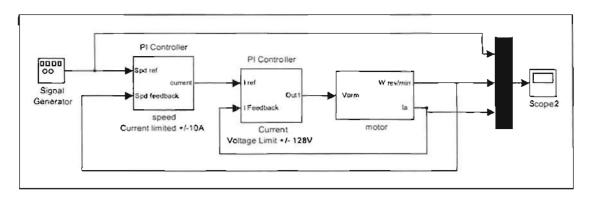

| 7.2.4       | Design and Simulation of Speed PI Controller          | 7-10 |

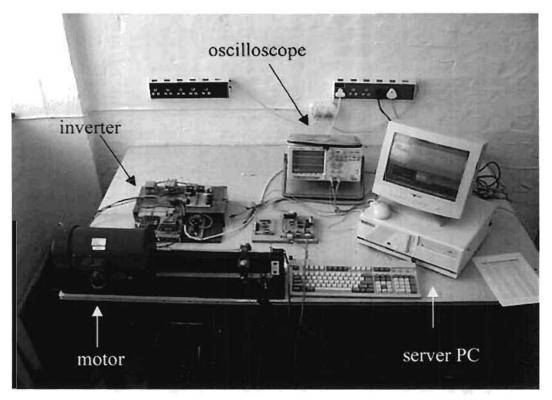

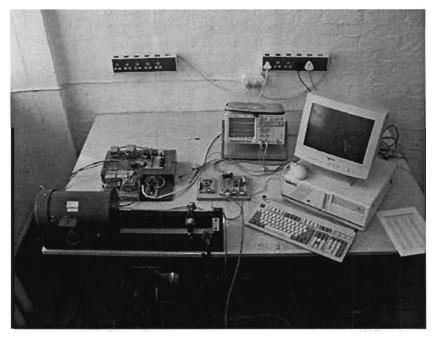

| 7.3. Dem    | onstration of the RADE ADC64 System                   | 7-12 |

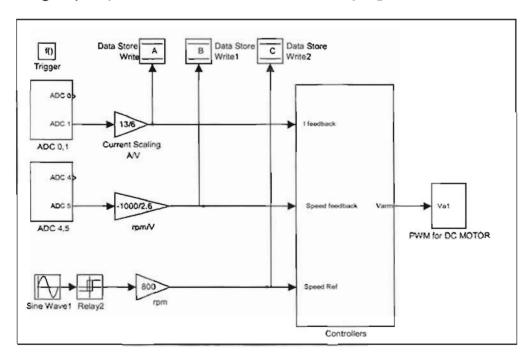

| 7.3.1       | Real-Time Prototyping with the RADE ADC64             | 7-13 |

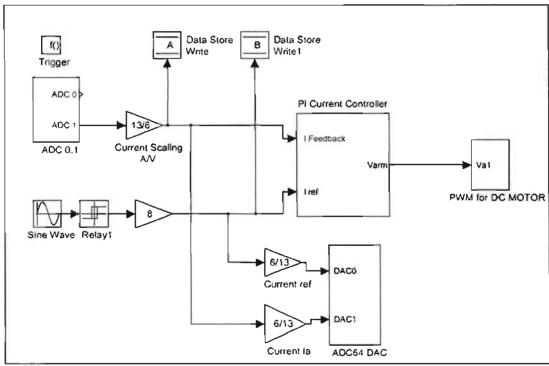

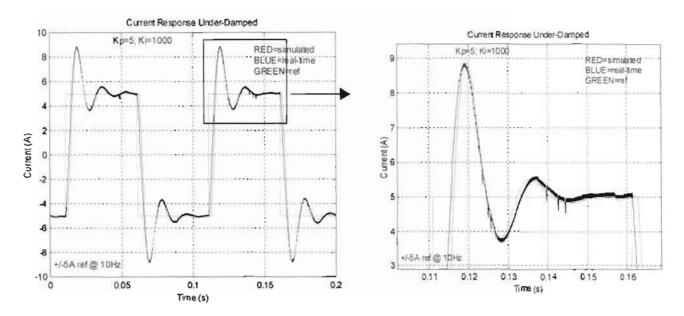

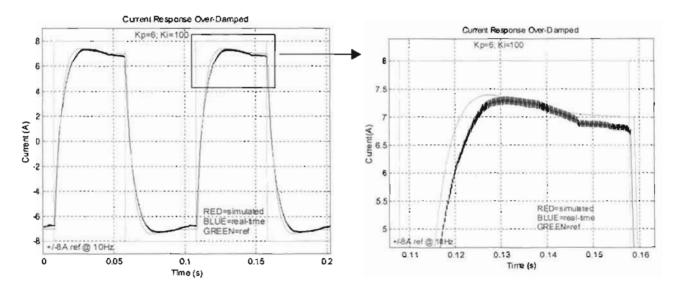

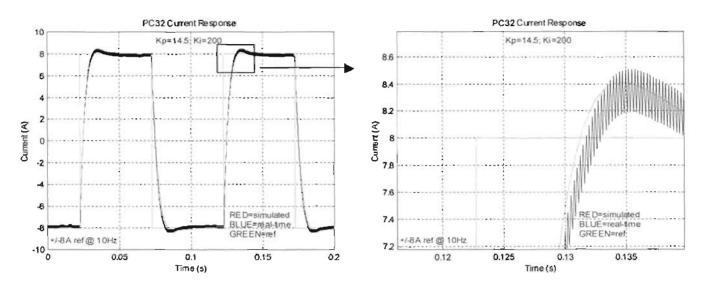

| 7.3.2       | DC Current Controller                                 | 7-15 |

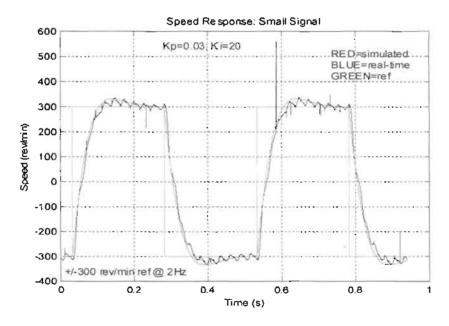

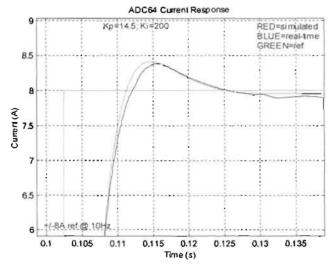

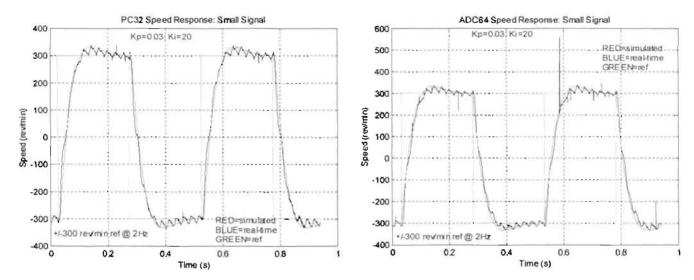

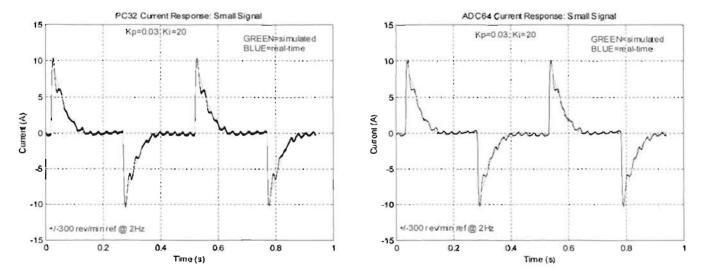

| 7.3.3       | DC Speed Controller                                   | 7-21 |

| 7.4. Dem    | onstration of RADE PC32 System                        | 7-26 |

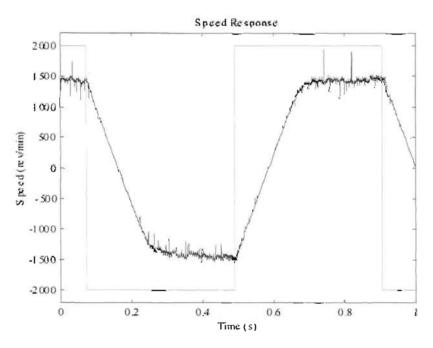

| 7.4.1       | DC Servo Speed Control                                | 7-26 |

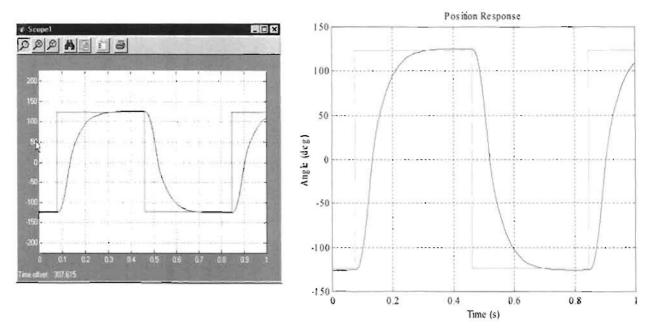

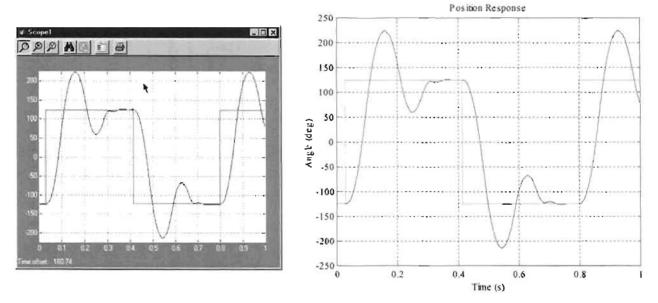

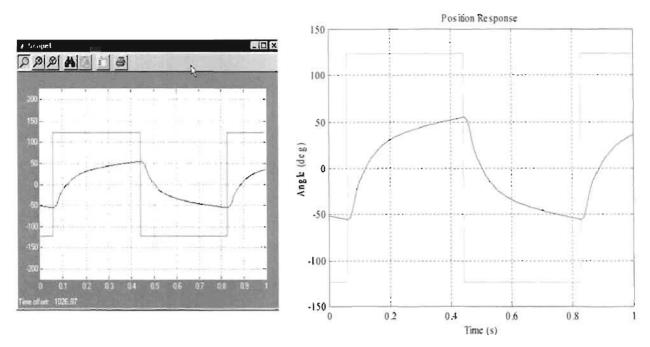

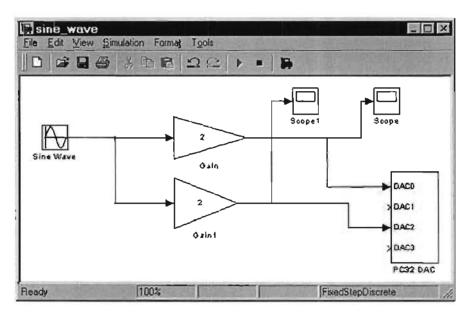

| 7.4.2       | Position Controller Experiment                        | 7-30 |

| 7.5. Con-   | clusion                                               | 7-34 |

| CHAPTER EIGHT: CONCLUSION                                        | 8-1     |

|------------------------------------------------------------------|---------|

| 8.1. General                                                     | 8-1     |

| 8.1.1 Role of the RADE Framework                                 | 8-1     |

| 8.2. Suggestions for Further Work                                | 8-2     |

| APPENDIX A: USER GUIDE                                           | .,1     |

| A.I. Installation Manual for RADE version 1                      | 1       |

| A.1.1 Installation of the RADE Components to Matlab directory    | 1       |

| A.1.2 Installation of Server Application                         |         |

| A.2. Sine Wave Example                                           | 3       |

| A.2.1 RADE PC32                                                  | 3       |

| A.2.2 RADE ADC64                                                 | 6       |

| APPENDIX B: A PROGRAMMER'S GUIDE TO THE INTERNAL WORKING OF I    | HE RADE |

| SYSTEMS                                                          | 1       |

| B.1. Modifications to The Mathworks External Mode Implementation | 1       |

| B.1.1 Default Mathworks External Mode Implementation             |         |

| B.1.2 RADE External Mode                                         |         |

| B.2. Server to Target Protocol                                   | 5       |

| APPENDIX C: EVALUATION OF MOTOR PARAMETERS                       | 1       |

| APPENDIX D: LISTING OF CODE FOR THE RADE PC32                    | 1       |

| D.1. Conversion Functions ext_convert_c3x.c                      | 1       |

| D.2. System Target File                                          | 13      |

| D.3. System Template Make File                                   | 14      |

| D.4. Device Driver Files                                         | 18      |

| D.4.1 ADC Blocks                                                 | 18      |

| D.4.2 DAC Block                                                  | 18      |

| D.4.3 PWM Block                                                  | 19      |

| D.4.4 Asynchronous Interrupt Support                             | 21      |

| APPENDIX E: LISTING OF CODE FOR THE RADE ADC64 | 1  |

|------------------------------------------------|----|

| E.1. System Target File                        | 1  |

| E.2. System Template Make File                 | 3  |

| E.3. Device Driver Files                       | 6  |

| E.3.1 ADC Blocks                               | 6  |

| E.3.2 DAC Block                                |    |

| E.3.3 PWM Block                                | 8  |

| E.3.4 Asynchronous Interrupt Support           | 9  |

| E.3.5 External Timers                          | 13 |

| APPENDIX F: DESCRIPTION OF CD                  |    |

|                                                | •  |

| REFERENCES                                     |    |

# TABLE OF FIGURES

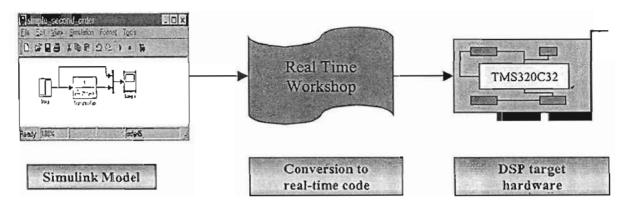

| Fig. 1.1: Mathworks rapid prototyping process                                   | 1-2  |

|---------------------------------------------------------------------------------|------|

| Fig. 2.1: Conventional real-time design                                         | 2-2  |

| Fig. 2.2: The rapid prototyping design                                          | 2-3  |

| Fig. 2.3: Hypersignal environment                                               | 2-5  |

| Fig. 2.4: Simplified operation of Mathworks RTW                                 | 2-6  |

| Fig. 2.5: dSPACE TDE toolset                                                    | 2-8  |

| Fig. 2.6: Rapid prototyping laboratory                                          | 2-9  |

| Fig. 2.7: Function diagram Quanser system                                       | 2-11 |

| Fig. 2.8: Functional operation of CSDE                                          |      |

| Fig. 2.9: Function diagram of ROGER the robot                                   |      |

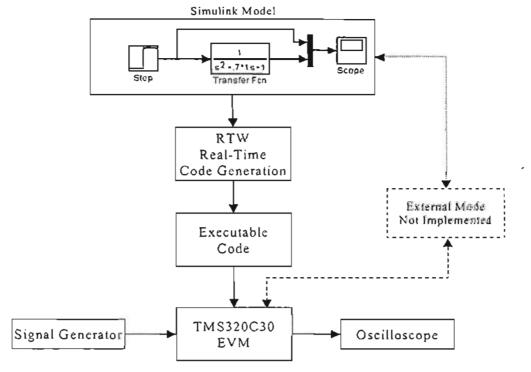

| Fig. 2.10: Functional diagram for TMS320C30 EVM RTW target                      |      |

| Fig. 3.1: Product range from The Mathworks                                      | 3-2  |

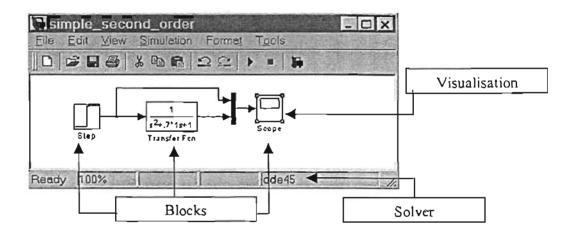

| Fig. 3.2: A Simulink simulation                                                 | 3-3  |

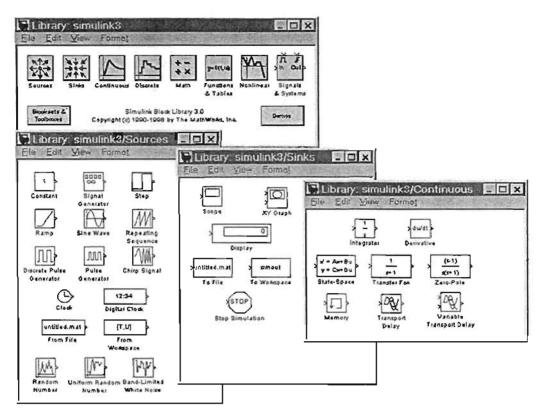

| Fig. 3.3: A sample of the common Simulink library blocks                        | 3-4  |

| Fig. 3.4: Simulink simulation parameters                                        | 3-5  |

| Fig. 3.5: The scope block output of the step response of the system in Fig. 3.2 |      |

| Fig. 3.6: An example of a subsystem                                             | 3-6  |

| Fig. 3.7: An example of a triggered subsystem                                   |      |

| Fig. 3.8: General model of a Simulink block [                                   |      |

| Fig. 3.9: Flow diagram of Simulink internals                                    | 3-8  |

| Fig. 3.10: How Simulink calls into a S-function                                 | 3-9  |

| Fig. 3.11: The flow diagram of writing and compiling a S-function               | 3-9  |

| Fig. 3.12: API function and their calling sequence                              | 3-10 |

| Fig. 3.13: Flow diagram of code generation process                              |      |

| Fig. 3.14: Object-oriented view                                                 | 3-14 |

| Fig. 3.15: Operation of the Target Language Compiler                            | 3-15 |

| Fig. 3.16: List of system target files                                          | 3-16 |

| Fig. 3.17: Flow diagram of the build process                                    | 3-23 |

| Fig. 3.18: Rapid prototyping program framework                                  | 3-24 |

| Fig. 3.19: Structure of model code                                              | 3-26 |

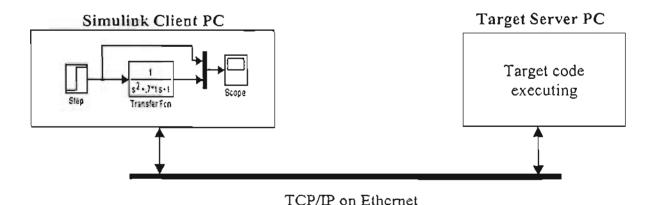

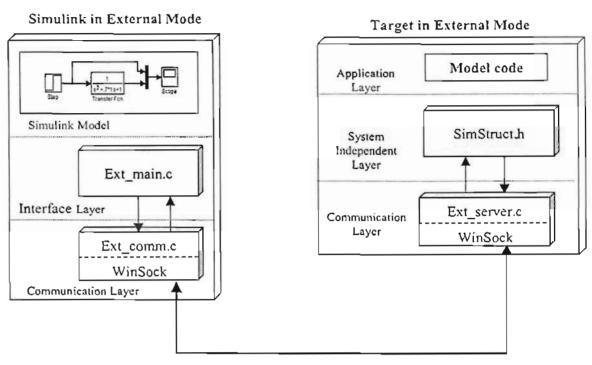

| Fig. 3.20: TCP/IP implementation of external mode                               | 3-27 |

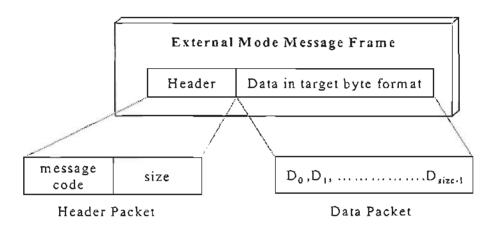

| Fig. 3.21: Message frame                                                        | 3-28 |

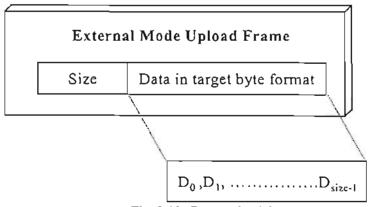

| Fig. 3.22: Data upload frame                                                    | 3-28 |

| Fig. 3.23: Simulink internals                                                   | 3-30 |

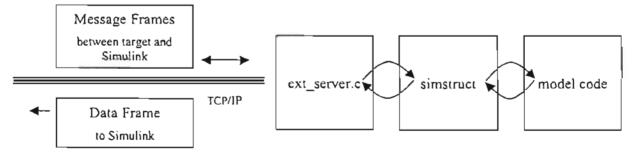

| Fig. 3.24: Target internals                                                     | 3-31 |

| Fig. 3.25: Message Transactions                                                 | 3-32 |

|                                                                                 |      |

# TABLE OF FIGURES

| Fig. 4.1: Mathworks TCP/IP external mode                          | 4-2  |

|-------------------------------------------------------------------|------|

| Fig. 4.2: CSDE external mode architecture                         | 4-2  |

| Fig. 4.3: RADE external mode architecture                         | 4-4  |

| Fig. 4.4:Zuma toolset                                             | 4-6  |

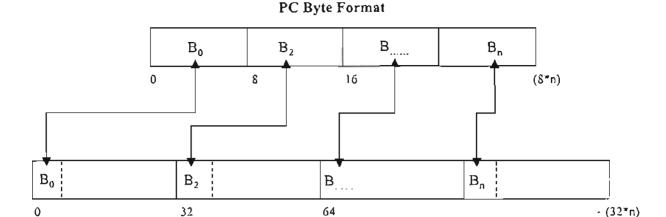

| Fig. 4.5: Byte format                                             | 4-10 |

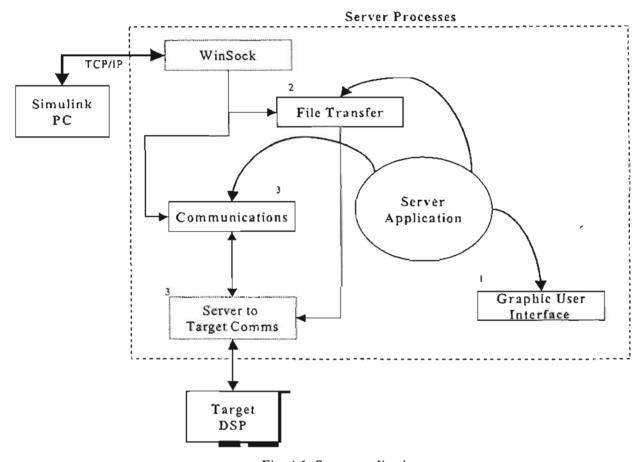

| Fig. 4.6: Server application                                      | 4-13 |

| Fig. 4.7: Server GUI                                              | 4-14 |

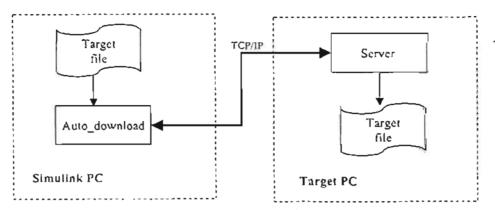

| Fig. 4.8: Functional representation of the file transfer process  | 4-15 |

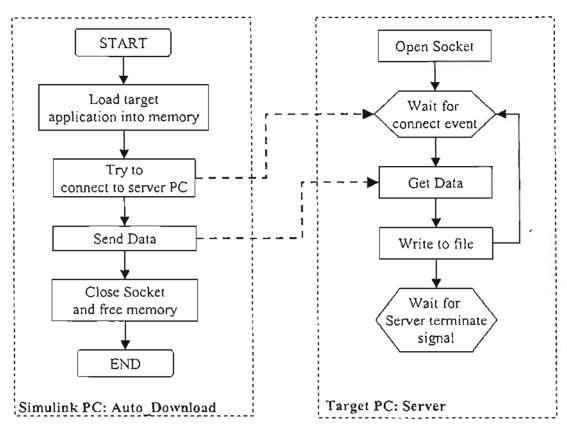

| Fig. 4.9: Flow diagram of file transfer process                   | 4-16 |

| Fig. 4.10: Flow diagram of RTI entry function                     | 4-18 |

| Fig. 4.11: Server to target communications                        |      |

| Fig. 4.12: Overview of Communication Channel                      |      |

| Fig. 4.13: Graphical representation of the Message Ports          | 4-21 |

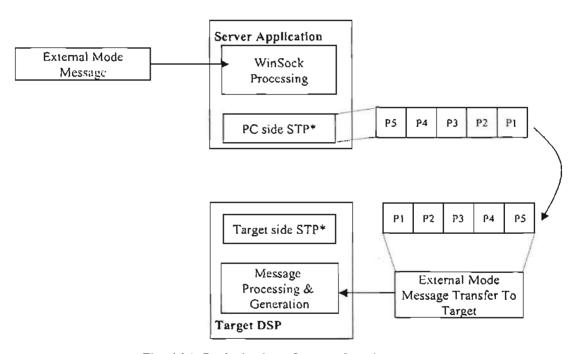

| Fig. 4.14: Packetisation of external mode messages                | 4-22 |

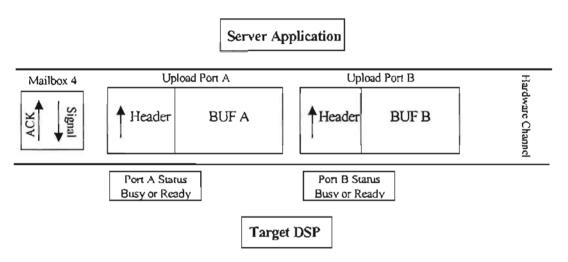

| Fig. 4.15: Graphical representation of the Upload Ports           | 4-23 |

| Fig. 5.1: Overview of RADE PC32 implementation                    | 5-1  |

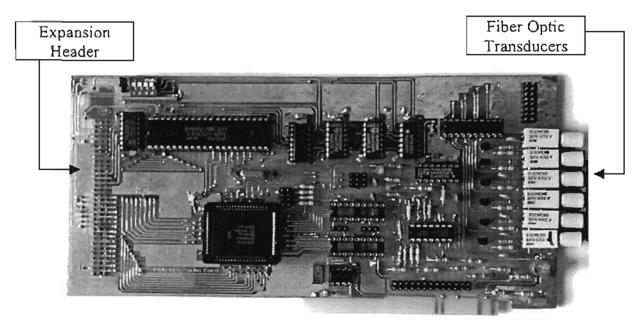

| Fig. 5.2: Photo of PC32 card                                      |      |

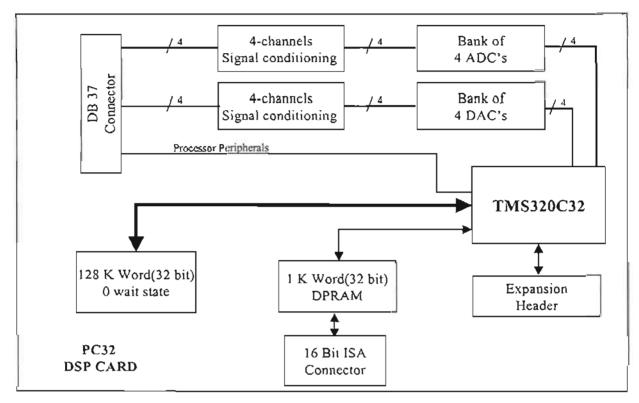

| Fig. 5.3: Functional diagram of the PC32 card                     |      |

| Fig. 5.4: ADC triggering                                          | 5-4  |

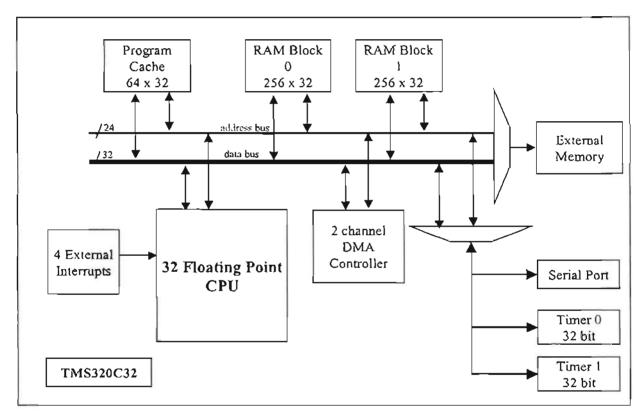

| Fig. 5.5: TMS320C32 block diagram                                 | 5-5  |

| Fig. 5.6: Photo of PWM card                                       | 5-6  |

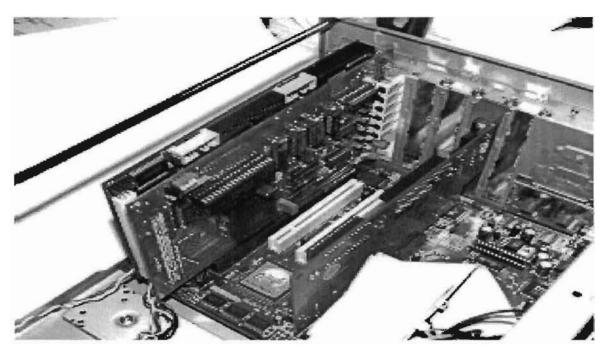

| Fig. 5.7: The DSP and PWM plug into the target PC                 |      |

| Fig. 5.8:Block diagram Of PWM card                                | 5-7  |

| Fig. 5.9: Device driver blocks for PC32                           |      |

| Fig. 5.10: Parameters for interrupt block                         | 5-12 |

| Fig. 5.11: Flow diagram for the modified Run-Time interface       | 5-13 |

| Fig. 5.12: Files used for external mode and STP                   | 5-15 |

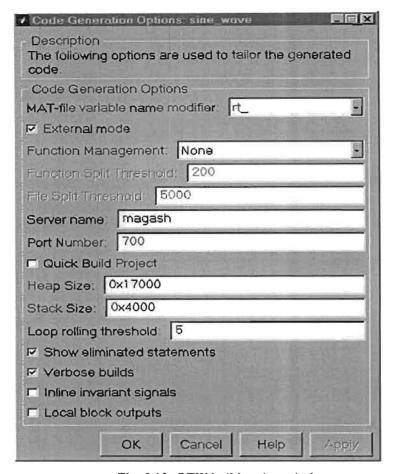

| Fig. 5.13: RTW build option window                                | 5-18 |

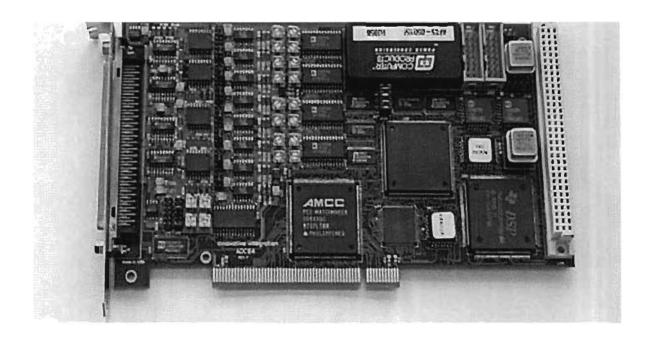

| Fig. 6.1 Photo of the ADC64 DSP card                              | 6-2  |

| Fig. 6.2 Functional diagram of the ADC64 card                     | б-3  |

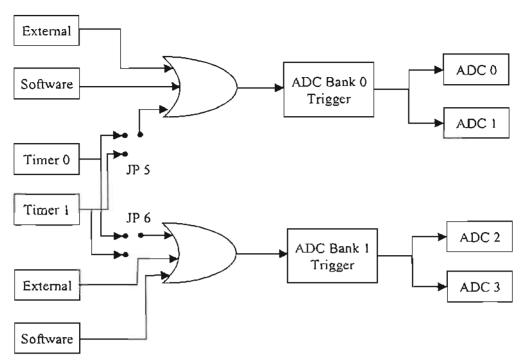

| Fig. 6.3: ADC trigger sources for the ADC64 card                  | 6-4  |

| Fig. 6.4: Device Drivers for the ADC64 card                       | 6-4  |

| Fig. 6.5:ADC trigger source selection                             |      |

| Fig. 6.6:Parameters for external timer Block                      | 6-7  |

| Fig. 6.7:Interrupt block parameters                               | 6-8  |

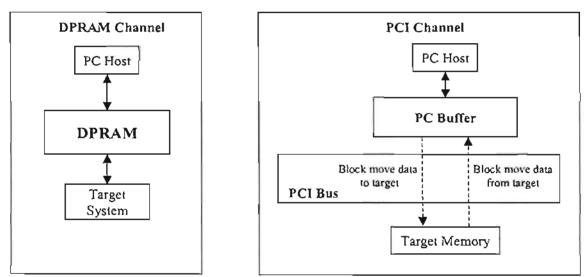

| Fig. 6.8: A comparison between DPRAM and the PCI bus              |      |

| Fig. 6.9: Files used for external mode and STP and the RADE ADC64 | 6-10 |

| T | ۱R | LF | OF           | FT | GU | IRES |

|---|----|----|--------------|----|----|------|

|   | ~  |    | $\mathbf{v}$ |    |    |      |

| Fig. | 7.37:Simulink model                 | 7-2 |

|------|-------------------------------------|-----|

| Fig. | 7.38: Subsystem 1 block             | 7-2 |

| Fig. | 7.39: Current response              | 7-2 |

| Fig. | 7.40:ADC64 Current sampling         | 7-2 |

| Fig. | 7.41: Small signal speed response   | 7-2 |

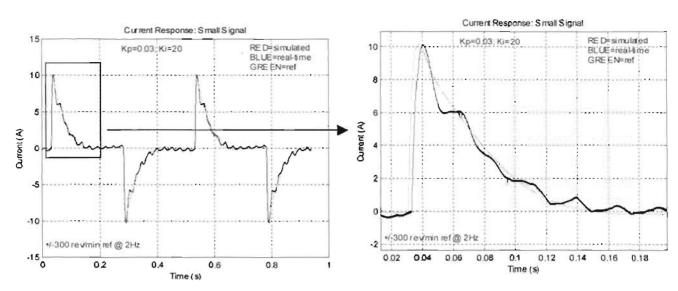

| Fig. | 7.42: Small signal current response | 7   |

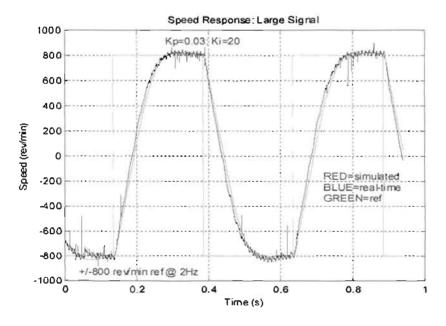

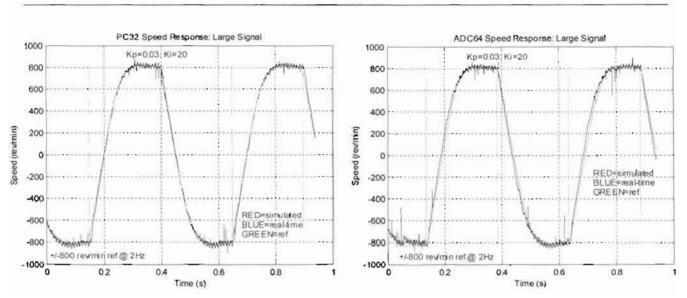

| Fig. | 7.43: Large signal speed response   | 7   |

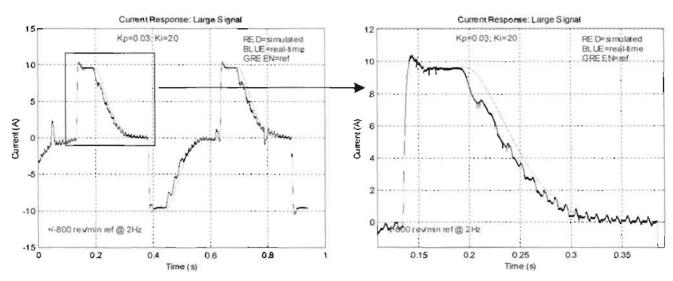

| Fig. | 7.44: Large signal current response | 7   |

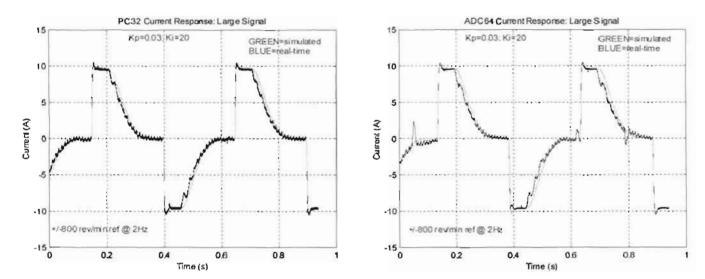

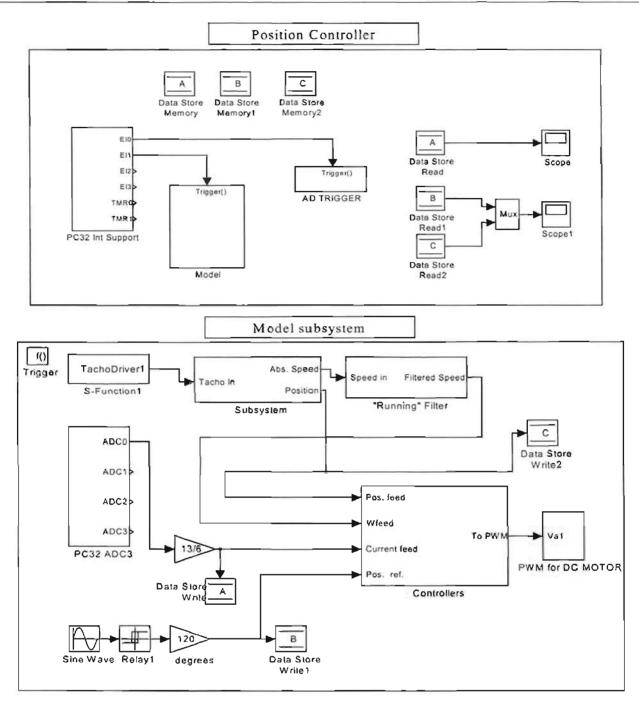

| Fig. | 7.45: Simulink model                | 7   |

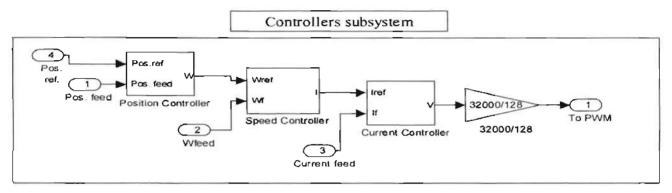

| Fig. | 7.46:The controllers subsystem      | 7   |

| Fig. | 7.47:Regulating position response   | 7   |

| Fig. | 7.48: Under damped response         | 7   |

| Fig. | 7.49: Over damped response          | 7-  |

## LIST OF ABBREVIATIONS

ADC Analogue to Digital Converter

API Application Program Interface

ASIC Application Specific Integrated Circuit

BSD Berkeley Software Distribution

DAC Digital to Analogue Converter

DLL Dynamic Linked Library

DMA Direct Memory Access

DPRAM Dual Port RAM

DSP Digital Signal Processor

FTP File Transfer Protocol

GUI Graphic User Interface

II Innovative Integration

IPC Inter Process Communications

ISR Interrupt Service Routine

MFC Microsoft Foundation Class

RADE Rapid Application Development Environment

RAM Random Access Memory

RPM Revolution per Minute

RTI Run-Time Interface

RTW Real Time Workshop

STP Server to Target Protocol

TCP/IP Transmission Control Protocol/Internet Protocol

TI Texas Instruments

TLC Target Language Compiler

VSD variable speed drive

# CHAPTER ONE: INTRODUCTION

#### 1.1. General

In our modern world the use of real-time systems has become commonplace in our homes, cars and workplaces. This is due to the reducing cost of microprocessors coupled with the phenomenal increase in processor bandwidth [AHMED1]. The use of DSP and real-time control is set to continue and engineering educators are therefore required to produce graduates that are equipped to tackle the challenges and technological changes in these fields [TQ2].

Teaching courses that rely on real-time system presents a dilemma to engineering educators, as the implementational details require students to be relatively well versed in software engineering concepts [GAN1]. This is further aggravated by the time constraint of presenting both theoretical course content as well as practical implementations. A point in case is the teaching of Control Systems. This is a challenging theoretical course that is fundamental to many engineering disciplines but is difficult to teach from a practical standpoint, as most modern day implementations rely on complex real-time processing hardware [FENG1]. A plausible solution to this problem is the use of Real-Time Rapid Prototyping Tools.

Rapid prototyping tools allow educators to concentrate on core concepts without being hamstrung by implementational details. Students can use these tools to experimentally validate theoretical assertions without needing to be experienced in software engineering [DSPACE5]. Rapid prototyping allows students from diverse engineering backgrounds to utilise sophisticated digital hardware to control/analyse real-time systems.

## 1.2. An Overview of Work Presented

The work presented in this thesis deals with the design, development and implementation of a rapid prototyping tool, which is the Rapid Application Development Environment (RADE).

The RADE system consists of three components:

- Simulink &[MATHWORKS2], which is a widely used graphical simulation package.

- Real Time Workshop (RTW)[MATHWORKS4], an add-on toolbox from The Mathworks, which converts Simulink, models into real-time code

• Target hardware platform that executes the real-time code.

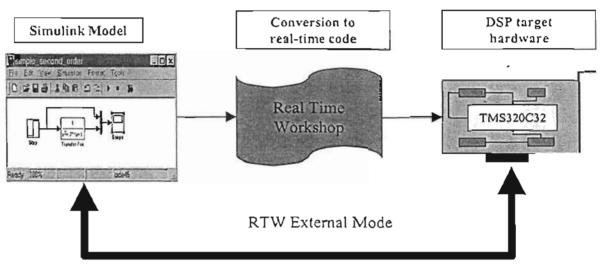

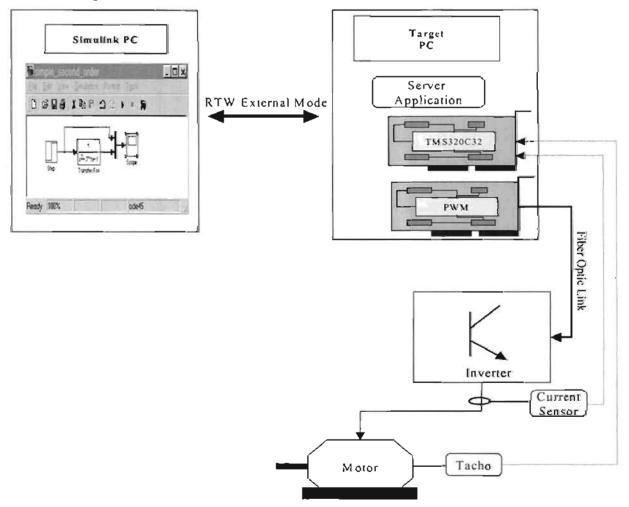

The RADE system, shown in Fig. 1.1 integrates the above components, and offers seamless generation of real-time code from Simulink models. This allows students with little expertises in software engineering, to utilise advanced DSP hardware. The advantage of this approach is that it allows students, to immediately apply concepts taught in courses like control systems, communications and robotics, to real-time systems and see first hand practical verification of theory.

Fig. 1.1: Mathworks rapid prototyping process

The RADE system features the following functionality:

1. Full network and standalone functionality

The system can operate in a standalone mode, whereby Simulink and the target DSP hardware reside on one workstation or in a network mode, whereby multiple users can access a single target DSP hardware. The latter scenario is ideally suited to the educational environment since numerous students can use one DSP card.

#### 2. Online Visualisation

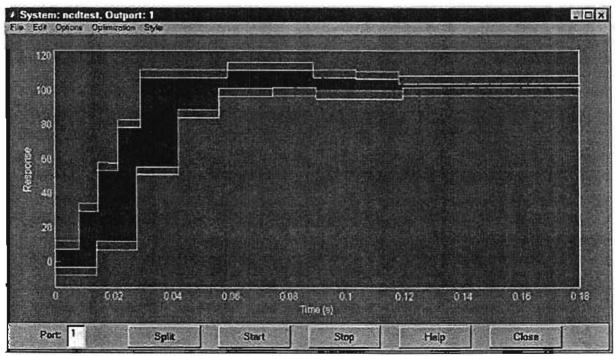

The RADE system is a world first to provide online data visualization using the Simulink scope block, for the TMS320C3x DSP. This allows various signals within a model, to be monitored when it is executing in real-time on the target hardware.

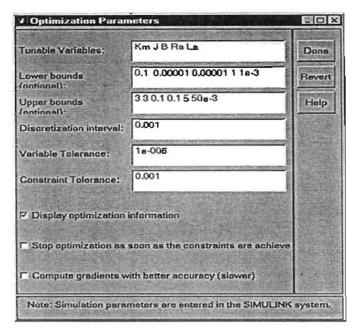

#### 3. Online Parameter Tuning

This feature allows for live changes to parameters within a model, while it is executing on the target hardware. It is especially useful for varying controller parameters and observing system responses. Concepts of controller stability and saturations are easily and quickly demonstrated by varying controller parameters.

#### 4. Multiple Target DSP platforms

The RADE system conforms closely to The Mathworks conventions and is therefore portable to various target platforms. The RADE has been successfully ported to, two DSP cards; the PC32 and ADC64. These cards use the TMS320C32 DSP and are manufactured by Innovative Integration.

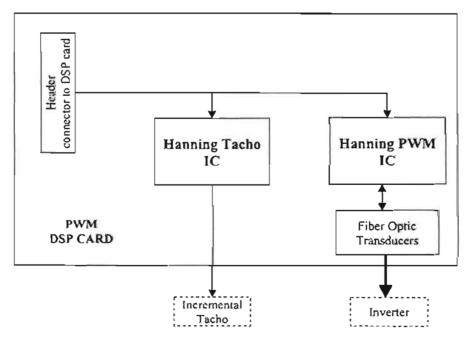

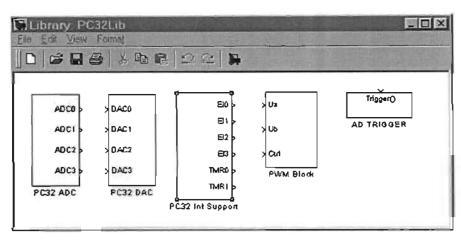

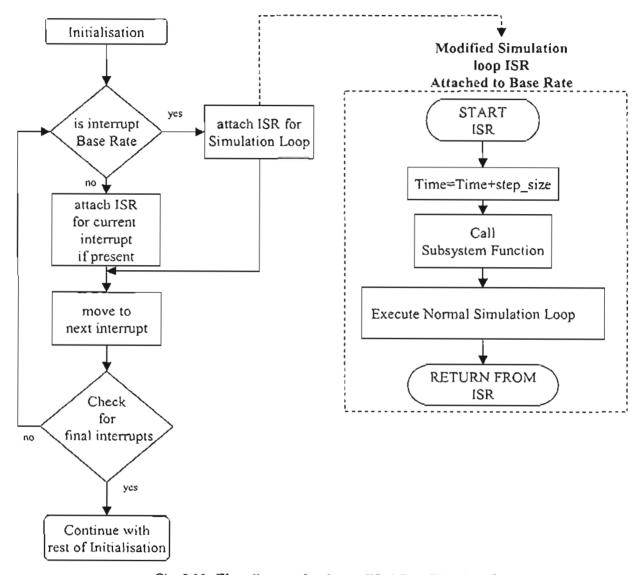

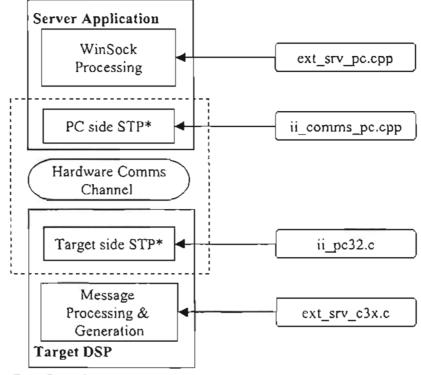

#### 5. In house build PWM I/O card

The RADE system was designed to serve a wide spectrum of applications, which also include Motion Control. Therefore a PWM add-on card was designed, to interface directly to the target DSP and provide PWM signal for an inverter. This reduces the processing burden on the target processor and allows for more complex real-time controllers to be implemented.

## 1.3. Thesis Sructure

Chapter 2 presents a literature survey of the current work in the Rapid Prototyping field and concentrates on educational applications. This chapter concludes with the context and purpose of the work presented in this thesis.

Chapter 3 presents background information on Simulink and the workings of the RTW.

Chapter 4 covers the system level design of the RADE framework. It highlights the modifications needed to The Mathworks RTW and details the components of the RADE framework.

Chapter 5 details the implementation of the RADE framework to the PC32 card.

Chapter 6 details the implementation of the RADE framework to the ADC64 card.

Chapter 7 provides a demonstration of the RADE system. An implementation of a DC motor current and speed is presented using the ADC64 and PC32 cards. In addition a DC motor position controller is implemented on the PC32 system.

Chapter 8 concludes this thesis and provides suggestions for further work.

#### 1.4. Publications and Contributions

During the course of the work presented in this thesis the following publications and contributions were made:

M. Pillay Greg Diana "A Design Tool To Facilitate a Matlab/Simulink Simulation, to Run in Real

Over a Networked DSP Card", Proceedings of the 8th Southern African

Universities Power Electronics Conference, Potchefstoom, South Africa

January 1999.

#### Worlds First Implementation of The Mathworks RTW-3 for the TMS320C32 Target

During the development of the RADE system software bugs were found in the Simulink internals and ,with the help of The Mathworks Support Centre, were corrected. The Mathworks support engineers also stated that this implementation was there first to use a non-PC byte compliant target within The Mathworks TCP/IP External Mode Architecture. Chapter 4 provides more details in this regard.

# CHAPTER TWO: LITERATURE SURVEY

#### 2.1. Introduction

The landscape of engineering education is being transformed by the advent of the Information Age. The availability of high-speed communication networks, powerful computing technology and advanced software are allowing engineering educators to provide students with a richer learning experience [TQ2]. Real-Time Rapid Prototyping<sup>1</sup> is one such technology that is impacting on the teaching of courses like control engineering, DSP and robotics. Engineering educators at numerous institutions across the world are starting to use rapid prototyping tools in their research and teaching syllabuses [KOZICK, STYLO1, GAN1].

This chapter describes the use and role of rapid prototyping in the research being conducted by the University of Natal's Motion Control Group and other researchers across the world. It presents a concise overview of The Mathworks rapid prototyping framework and a general review of both commercial and academic implementations derived from this framework. The main aim of this chapter is to review the use of The Mathworks rapid prototyping framework from an educational perspective.

Finally the author contextualises the purpose and role of his work and develops project goals for the development of the RADE system.

# 2.2. Real Time Rapid Prototyping

In a description of rapid prototyping it is informative to first outline the conventional methodology for designing real-time systems and then compare it to the rapid prototyping approach. This is presented in the next two sections.

<sup>1</sup> Any reference to Rapid Prototyping in this thesis will exclusively deal with Real-Time Rapid Prototyping.

#### 2.2.1 The Conventional Real-Time Design

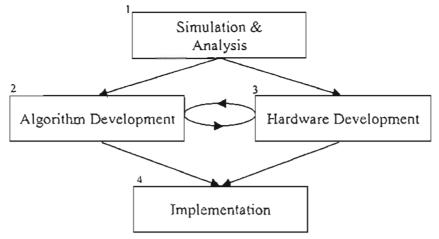

Fig. 2.1: Conventional real-time design

The conventional design process of a real-time system is shown in Fig. 2.1. This normally requires multiple design teams and involves the following four stages:

#### 1. Simulation and Analysis

At this stage the system to be designed is evaluated and different control strategies are simulated. The results are then analysed and a feasible specification is passed on to the next stage.

#### 2. Algorithm development<sup>2</sup>

From the specifications the software team develops an appropriate algorithms, which traditionally involve C and some low level programming.

#### 3. Hardware development

The hardware team is responsible for the designing of the hardware platform on which the final system will run.

#### 4. Implementation phase

Once the hardware and software teams have produced their components the implementation team is responsible for the integration and testing. If the system fails during the test cycle the design processes is restarted at the stage where the problem is anticipated to be.

In the conventional approach, different tools and expertise are utilised in the development process, with control engineers being used in the first stage and hardware and software engineers being involved in the remaining stages. This approach is very time and labour intensive with each design

<sup>&</sup>lt;sup>2</sup> This stage can run in parallel with hardware development.

cycle being costly. A further disadvantage is that code produced by the software teams tend to be difficult to reuse and incorporate in new systems. The advantage of the conventional approach is that the resulting system can be both cost and performance optimised for volume production.

#### 2.2.2 The Rapid Prototyping Approach

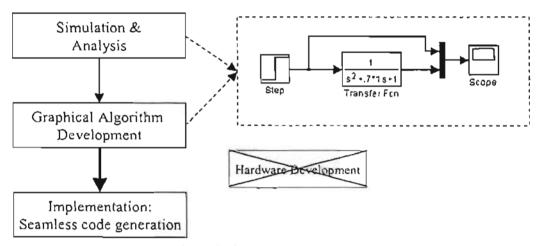

Fig. 2.2: The rapid prototyping design

In the rapid prototyping approach shown in Fig. 2.2, it is evident, that the hardware stage has been removed allowing a seamless step from algorithm to implementation. Further more the algorithm stage uses a high level graphical language [MATHWORKS6]. The appeal of rapid prototyping over the conventional approach is that:

- The user need not be skilled in software engineering.

- There is no need for multi-disciplinary design teams.

- There is a dramatic time saving.

The rapid prototyping approach eliminates the hardware development stage by using generic hardware platforms. These platforms consists of DSP or microprocessors, with I/O devices that interface to the sensors and actuators on the plant being controlled [DSPACE5].

From the above discussion it is apparent that rapid prototyping is not a replacement for the conventional approach but rather an alternative that allows the designer more flexibility at the simulation and analysis stage. Rapid prototyping applications provide the user with more functionality and less complexity. They do not compete with the conventional approach but are rather an augmentation to it.

# 2.2.3 The Role of Rapid Prototyping in Education

Rapid prototyping in an educational context is targeted towards courses that rely on real-time systems

[SADASIVA1]. These include control systems, robotics and DSP to name a few. There are both teaching and research applications with research being further split between users and developers of rapid prototyping tools<sup>3</sup>.

The appeal of rapid prototyping is that it now frees the user from the need to be highly skilled in software engineering and allows advanced hardware to be used by a "lay" audience. Researchers using rapid prototyping are freed to concentrate on their applications rather than being distracted by the peripheral hardware and coding design issues. Educators are able to present better courses, as students are able to immediately evaluate theoretical concepts experimentally.

The teaching of control system is a good example of a theoretically intensive course that benefits from rapid prototyping tools. Lecturers can concentrate on the core concepts that are independent of implementation issues while at the same time allowing students to apply these concepts to a live real-time systems. The traditional design of a motor controller, which normally ends with students merely simulating it, can now be followed up with immediate implementation. Students can also investigate the practical issues of controller stability and plant saturation, which are difficult to appreciate without a live system.

Another aspect that needs consideration in the development of rapid prototyping educational tools is their ability to be networked. Network features provide value adding by maximising utilisation of expensive resources<sup>4</sup> while also minimising total system costs. Further, with Virtual Laboratories<sup>5</sup>, [HAMMANN1, HUGH1, REID1] based on Internet technologies gaining in popularity, it makes a compelling argument to providing network supported rapid prototyping tools that can be easily incorporated into such laboratories.

Within the rapid prototyping arena there are various tools and in the next two sections products from Hyperception and The Mathworks are reviewed, as they are both being used by the Motion Control Group.

<sup>3</sup> The work in this thesis falls into the rapid prototyping development category.

<sup>&</sup>lt;sup>4</sup> These resources include the DSP target hardware and external plant being controlled

<sup>&</sup>lt;sup>5</sup> Virtual Laboratories use Internet technology to allow student 24-hour access to experimental apparatus.

## 2.2.4 Hypersignal

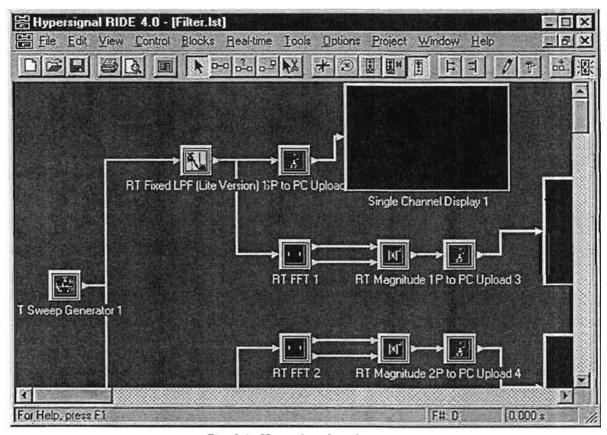

Fig. 2.3: Hypersignal environment

Hyperception Inc. produces the Hypersignal rapid prototyping tool, which uses a graphical environment for algorithm development as shown in Fig. 2.3. It however lacks a comprehensive simulation environment but allows algorithms to be tested on the PC platform before being executed on the intended hardware platform. This tool is targeted mainly for advanced DSP development and is provided with drivers, which support numerous third party DSP cards [BLERK1].

Hypersignal is being used by the Motion Control Group to implement and evaluate motion control applications and tools. A Variable Speed Drive (VSD) test bed tool has been developed to evaluate the performance of VSD's for different load conditions [WALKER1]. Worthmann [WORTHMANN1] evaluated the use of an artificial intelligence algorithm for the control of a boost rectifier. Both these researchers have stated that a considerable portion of their time was spent customising<sup>6</sup> the Hypersignal environment for their applications. Further, simulations of these systems were also performed using other packages.

<sup>&</sup>lt;sup>6</sup> This involves the hand coding of application specific blocks that can then be used with the Hypersignal environment.

The Hypersignal package provides a powerful algorithm development tool that concentrates on traditional DSP development and is ideally suited to research applications. However it lacks simulation and analysis components and requires a steep learning curve, making the system unfeasible as a teaching tool.

#### 2.2.5 The Mathworks Rapid Prototyping Framework

Fig. 2.4: Simplified operation of Mathworks RTW

The Mathworks provide the Real Time Work (RTW) [MATHWORK4, 6], which is integrated with the widely used Simulink environment [PAI1, POUS1]; together they form an open architecture rapid prototyping framework. Fig. 2.4 shows a simplified representation of the operation of the RTW, which consists of:

- Simulink, which is a graphical simulation and analysis tool.

- The RTW, which is a toolset and framework responsible for the entire rapid prototyping process.

- Target hardware is the platform on which the generated code runs. The open architecture of the RTW allows users to incorporate third party hardware within the RTW. This process is referred to as RTW targeting<sup>7</sup>.

- RTW External Mode is a feature that allows Simulink to connect to the target platform, whereby target operation may be controlled from within the Simulink environment. This feature allows for:

- Communication to remote targets.

- Control of start/stop actions on the target.

Some of the RTW targets supported by The Mathworks are: DOS real time; Windows 95/98/NT; VxWorks

#### • On-line parameter tuning and data logging.

Due to The Mathworks open architecture both academic and many commercial developers have extended the RTW to incorporate their custom hardware platforms. From the literature [KOZICK, STYLO1, GAN1, TQ1, DSPACE1, 2, 5] there are namely two approaches to use the RTW, either to use commercial products or to develop in house implementation. Both approaches provide viable educational tools, and the Motion Control Group has opted for in house solutions, as development of rapid prototyping tools is one of its active research objectives.

Sections 2.3 and 2.4 respectively, provide a look at some of the commercial and academic solutions available. These sections highlight the operation and general feedback from the use of these tools in both the research and teaching environments.

## 2.3. Third Party Tools Based On The Mathworks RTW

This section reviews commercial solutions based on the RTW framework and concentrates on companies that are providing viable educational tools.

#### 2.3.1 dSPACE

dSPACE GmbH<sup>s</sup> is German company that produces the Total Development Environment (TDE) [DSPACE1, 4, 5] rapid prototyping toolset. The TDE is based on the RTW and is targeted at both commercial and academic environments. It consists of the five components, shown in Fig. 2.5 and is explained below.

1. The Mathworks RTW has been explained in section 2.2.5

#### 2. Cockpit

This utility replaces Simulink's external mode control, but affords user similar functionality to interface to the target hardware for parameter tuning and visualisation. Using the Cockpit tools users can develop custom GUIs that contain graphs, gauges, slider gains, knobs, etc.

#### 3. Тгасе

This utility is a digital oscilloscope, which allows the user to get time histories of block outputs.

#### 4. MLIB and MTRACE

Theses are Matlab toolboxes from dSPACE that provide similar features to the Cockpit and Trace utilities from within the Matlab environment. The purpose of these toolboxes is to allow the use of Matlab analysis tools for on-line, real-time data

<sup>8</sup> www.dspace.com and www.dspace de

Matlab

Simulink

analysis in applications like system identification and control optimisation.

Fig. 2.5: dSPACE TDE toolset

#### 5. Real-Time Hardware

dSPACE provides a range of hardware processor cards that consist of either DSP or microprocessors processing elements, with combinations also available. These cards use either the Texas Instruments DSPs or DEC ALPHA microprocessors [DSPACE2, 3]. In addition I/O cards are provided that interface directly to processor cards, and connect to plant sensors and actuators. There are also Ethernet network cards that allow dSPACE target platform to operate in network environments.

# 2.3.2 Use of dSPACE in Engineering Education

dSPACE tools are being actively used at numerous academic institutions<sup>9</sup>. This section provides a review of some of this work and gives researcher's and student's opinion of these rapid prototyping tools.

<sup>&</sup>lt;sup>9</sup> Bucknell University [KOZICK1], The Mechatronics Laboratory at the Royal Institute of Technology [FENG1], University of Girona, [POUS1], University of Technology, Nanyang Singapore [GAN1].

Bucknell University [KOZICK1] USA has incorporated dSPACE tools into several of their courses, which included:

- Exploring Engineering, a first year introductory course.

- Control systems.

- DSP.

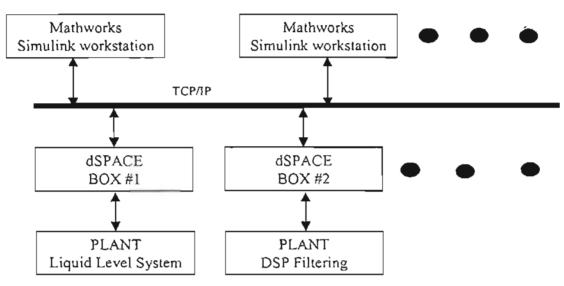

A functional diagram of the rapid processing laboratory is shown in Fig. 2.6. The emphasis at Bucknell is to allow a large volume of student to experiment with a wide variety of real-time application<sup>10</sup>. This is accomplished by using a network environment.

Fig. 2.6: Rapid prototyping laboratory

The experiences at Bucknell have shown that rapid prototyping has allowed under-graduates to access advanced real-time applications, which give the students a greater appreciation and understanding of theoretical courses.

At the Mechatronics Laboratory at the Royal Institute of Technology [FENG1] in Sweden, Prof Jan Wikander has been using dSPACE tools for a masters level control course. His reasons for using rapid prototyping tools are that they bridge the gap between the theory of automatic control and implementation issues; students from a mechanical engineering background, with limited advanced software experience are able to implement real-time control systems. Further more the Simulink environment lends itself to an easier understanding and visualisation of control system models. Feedback from students has shown that they have positively received the dSPACE tools and Prof. Wikander's controls course.

<sup>&</sup>lt;sup>10</sup> These applications include: a liquid level control system; servomechanisms for position of laser pointing devices; magnetic levitation of a metal ball; various DSP filtering applications.

The work by Sadasiva etal [SADASIVA] and Virvalo etal [FENG1], presented below, shows a different application for dSPACE tools. These researchers use rapid prototyping in their actual research.

Sadasiva etal [SADASIVA1] have used dSPACE tools to evaluate various PWM control algorithms<sup>11</sup>. dSPACE tools have allowed them to quickly implement different control algorithms and evaluate their performances. Sadasiva etal have stated that rapid prototyping tools have dramatically reduced their experimental time from months to a single week.

Prof Virvalo [FENG1] and colleagues from the Institute of Hydraulics and Automation in Tampere, have used the dSPACE toolset to evaluate several controllers, which included; one degree of freedom pneumatic servo drive; one degree of freedom hydraulic servo drive; two degree freedom hydraulic crane. Their feedback shows that the dSPACE toolset provides a powerful platform to implement complicated controllers with relative easy.

From the above discussion it is evident that dSPACE provides a useful rapid prototyping toolset for both research and teaching applications. The only notable drawback with this toolset is cost and learning curve involved with the use of the Cockpit and Trace utilities [STYLO1].

## 2.3.3 Complete Experimental Solutions

Quanser Consulting, Inc<sup>12</sup> [WINCON1] and TecQuipment Limited<sup>13</sup> [TQ1] are two of several companies that provide complete (canned) experimental apparatus used in the teaching of control systems and aligned fields. Their solutions are based on the RTW framework and are mainly targeted for teaching applications. Both Quanser and TecQuipment provide similar solutions and it is sufficient for the purposes of this thesis to discuss only one: Quanser was chosen as they provide more information on their products at their website.

| Linear Experiments     | Rotary Experiments    | Specialty Experiments                |

|------------------------|-----------------------|--------------------------------------|

| Linear Position Servo  | Rotary Position Servo | 3 Degree of freedom (DOF) helicopter |

| Inverted Pendulum (IP) | Ball and Beam         | 2 DOF helicopter                     |

| Self Erecting IP       | Rotary IP             | Magnetic levitation                  |

| Linear Gantry Crane    | Double IP             | Planar Rotary IP                     |

| Double IP              | 2 DOF IP              | Coupled Tanks                        |

<sup>&</sup>lt;sup>11</sup> Theses algorithms include: PI voltage controller cascaded with predictive current control; Model based voltage control cascaded with predictive current control. PI voltage controller cascaded with Vector current control.

<sup>12</sup> www.quanser.com

<sup>13</sup> www.tq.com

WinCon Server WinCon Server WIN 95, Matworks WIN 95, Matworks Simulink Simulink Remote User #1 Remote User #2 TCP/IP WinCon Client WinCon Client PC #1 PC#2 Quanser Plant Quanser Plant e.g. Linear Inverted e.g. Rotary Inverted Pendulum Pendulum

Table 2-1: List of experimental apparatus from Quanser

Fig. 2.7: Function diagram Quanser system

Quanser provide a wide range of experiments, which include, linear; rotary; and speciality experiments: a list is shown in Table 2-1. A functional diagram of the Quanser networked WinCon system is shown in Fig. 2.7, which consists of a WinCon server that is responsible for interfacing to Simulink and WinCon client, which is the real-time harness that runs generated model code<sup>14</sup>. An interesting feature of the systems from Quanser and TecQuipment is that they both use the soft real-time functionality of the Windows platform to execute target code (PC I/O cards are used to interface to external plants.). This technique minimises system cost and complexity by eliminating the DSP hardware. The drawback of this approach is that:

- The soft real-time makes sampling and latency times unpredictable 15.

- The rigid interface requirements limit the use of user designed custom plants.

- The PC platform also diminishes the application of these systems to courses that require the student to get DSP and embedded system experience.

# 2.4. Academic Developments with RTW

# 2.4.1 Control System Development Environment

The Control System Development Environment (CSDE) was developed for the Motion control

<sup>14</sup> WinCon can also run as a standalone system, whereby the WinCon server and client run on one PC.

<sup>15</sup> While the Window platform does not provide hard real-time functionality, it is being increasingly used in industrial applications that do not have strict timing specifications.

Group by Stylo and represents the group's first implementation of an in house rapid prototyping tool, and is therefore used as a reference point to the development of the RADE system. This section reviews the CSDE environment.

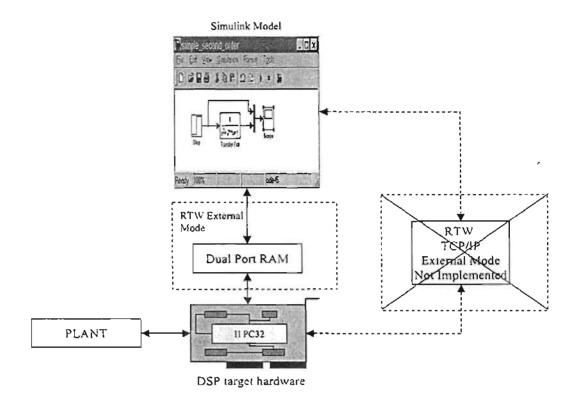

Fig. 2.8: Functional operation of CSDE

The CSDE is a cost effective rapid prototyping environment for both research and teaching application. The CSDE uses Simulink 2.2 and RTW 2.0<sup>16</sup> and provides the following functionality:

- Seamless code generation

- On-line parameter tuning

- External visualization utility

- Support for the Innovative Integration PC32 DSP card

- Asynchronous interrupt support

A functional representation of the CSDE<sup>17</sup> is shown in Fig. 2.8 and from this figure the following observation can be made:

The network support of the RTW is replaced by DPRAM communication technique, which makes CSDE a solely standalone system.

The standalone impediment did not however affect the operation of CSDE and it was well received by

<sup>&</sup>lt;sup>16</sup> CSDE does not operate with newer versions of the RTW as The Matworks have updated the internal workings of the RTW.

<sup>&</sup>lt;sup>17</sup> Further details on the internals of the CSDE system are presented in chapter 4.

under-graduate students that used the system in their final year design course. Shawn Sturgeon [STURGEON1] implemented Field Oriented Control drive for an induction motor and Lynden Moodley [MOODLEY1] implemented a DC motor position controller. Both these projects would not have been feasible if it had not been for rapid prototyping tools. Additional support for rapid prototyping is that both students found control systems a theoretical abstract subject, with very little appreciation for its practical uses. This however changed during the course of their design projects as first hand experimentation allowed them to get to grips with control theory. This new found understanding culminated in them both wining design awards in their respective years

#### 2.4.2 Work at Other Academic Institutions

The Mathworks RTW framework has been well received by other academic institutions, which have also opted to develop in house RTW targets. This section presents a review of some of these developments and how they were incorporated into course syllabuses at these institutions.

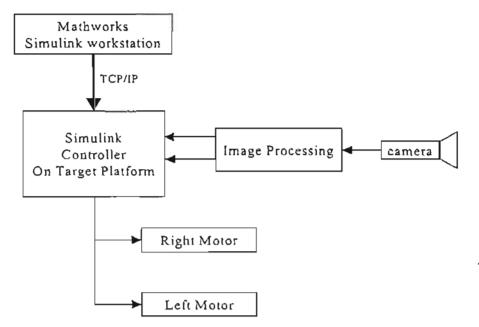

At the University of Girona, [POUS1] Catalonia Spain, Pous etal implemented a novel approach for a control system laboratory experiment in which they have used a robot named ROGER. A functional diagram of ROGER is shown in Fig. 2.9. The image processing system<sup>18</sup> is used to provide XY coordinates of a target object. This information is fed to a Simulink designed controller that provides the actuators signals for the left and right motors. The objective of the controller is to track a moving target while maintaining a specified distance. The ROGER experiment uses a PC platform<sup>19</sup> to implement the real-time target code and is aimed at allowing students to test different control algorithms easily without much emphasis placed on the underlying coding. This experiment incorporates both the simulation and live testing, which is an advantage of the Simulink environment.

<sup>&</sup>lt;sup>18</sup> This image processor is done on an independent processor and only the XY coordinates are feed to Simulink.

<sup>&</sup>lt;sup>19</sup> Pous etal did not specify if a DOS or Windows real-time target was used. It is the author's opinion that a DOS target was used, as it is a standard component of the RTW and provides hard real-time specifications, with a maximum sampling frequency of 400KHz.

Fig. 2.9: Function diagram of ROGER the robot

At the University Mining and Metallurgy, [GREGA1] Krakow Poland, Grega etal have built a RTW windows target. Their implementation targets Windows 95/98/NT platforms with the emphasis of their work to evaluate the real-time performance of the windows platform. This in house windows target achieved a maximum usable sampling time of 10ms<sup>20</sup> and a latency of around 80µs. This windows target is feasible for soft real-time<sup>21</sup> experiment but lacks the precision needed for hard real-time applications. The poor performance of this system is evident by Grega etal recommending the use of a commercial windows target, RT-CON by InTeCo Ltd, which provides better timing specifications.

At the University of Technology, Nanyang Singapore [GAN1], Gan etal have implemented a RTW target for the Texas Instruments TMS320C30 EVM board. The emphasis of this work was to produce a bare bones low cost DSP rapid prototyping teaching solution. A functional diagram of their solution is shown in Fig. 2.10. From this figure it is evident that the RTW external mode is not supported, as a result no on-line parameter tuning or visualisation will be possible. Gan's etal rationale for not supporting external mode is that quick repetitions of the RTW build process can be performed to change parameters, while an external oscilloscope can be used for visualisation. By using this technique a dramatic reduction in target complexity is achieved, albeit at the sacrifice of functionality. This system has been used in a DSP course at Nanyang University and allowed students to implement theoretically challenging DSP applications in short laboratory sessions. This would not have been

<sup>&</sup>lt;sup>20</sup> Using the Windows WIN32 API a maximum of sampling time of 1 ms can be achieved using TIMER objects (ring 3). It is also possible to use PC's 8254 timer for higher sampling time but Grega et al did not do this.

<sup>&</sup>lt;sup>21</sup> Soft real-time applications don't require strict specification on: sampling time; interrupt latencies; and interrupt preemption and priorities.

possible without the use of rapid prototyping tools and student's feedback has shown a positive response to this method of teaching.

Fig. 2.10: Functional diagram for TMS320C30 EVM RTW target

## 2.5. Context of Work Presented in this Thesis

From the preceding sections, it is evident that The Mathworks RTW is being actively used in commercial and academic, educational endeavours. The work undertaken in this thesis follows in this vain and is targeted at educational applications. This section highlights the purpose and context of this work and finally ends with a summary of project goals.

#### Is this work mere duplication?

NO. Rapid prototyping and more specifically the RTW are active research topics, in which the Motion Control Group has been involved in from 1996 with the development of the CSDE system. Rapid prototyping is making significant inroads in engineering education and other institutions are also investigating its uses [GAN1, GREGA1, POUS1]. The Motion Control Group as well as other academic institutions are also opting to develop in house rapid prototyping solutions that are based on the RTW framework. This route allows the researcher the flexibility to develop solutions around their courses and they are not hamstrung by rigid solutions similar to those produced by Quanser and TecQuipment.

The RTW workshop as a rapid prototyping framework is allowing interesting developments in the field of engineering education and therefore warrants the attention of any academic institution intent on using modern approaches to teaching. The Motion Control Group is therefore actively contributing to this process by the development of new RTW targets. Notwithstanding this, the RTW itself is an ever-changing framework, which allows greater functionality with every version update and the Motion Control Group is in an ideal position to capitalise on new developments in this field. A point in case is The Mathworks development of rapid prototyping tools for FPGA's. These tools are being incorporated into the RTW framework and in the not too distant future it will help to drastically reduce development time for FPGA and hybrid FPGA and DSP systems<sup>22</sup> [GORDON1].

The CSDE was the Motion Control Group's first attempt to use the RTW framework as a rapid prototyping tool, but has been outdated with the 1999 release of Simulink 3 and the RTW 3. The Mathworks constantly upgrades the RTW and there have been significant changes and improvements from RTW version 2 to 3. As a result tools based on the RTW have to be constantly maintained and upgraded. Consequently a methodology is needed to ease version upgrades and this was not provided with the CSDE system. The design approach adopted for the CSDE system was to provide an operational system while minimising system complexity. This resulted in Stylo [STYLO1] removing network support and not adhering to The Mathworks conventions, as a result CSDE met the operational criteria but lacked the framework requirements for revision changes and inclusion of other DSP cards<sup>23</sup>. In the development of the CSDE system no attempt was made to document the internal workings of the RTW in respect of the TCP/IP external mode implementation. While this did not impede the operation of the CSDE system it did hinder revision changes, as The Mathworks implements revisions using the TCP/IP external mode framework. This thesis aims to redress these issues and provide a system that adheres closely with Mathworks conventions.

#### 2.5.1 Categories of RTW Targets

For the RADE system to be properly contextaulised it is necessary to group work in this field into different categories of RTW targets. This allows for an appreciation of which category the RADE system is targeting and the intended functionality. Developments with the RTW target can be categorised into namely types:

#### 1. High-End Systems

<sup>&</sup>lt;sup>22</sup> The University of Natal's Radio Access and Transmission Centre is currently involved in CDMA research and uses FPGA to implement high-speed signal algorithms. It is therefore envisaged that the RADE framework will be expanded to accommodate FPGA targets.

<sup>&</sup>lt;sup>23</sup> CSDE only supports the PC32 DSP card

These systems use targets with powerful real-time OS's and have either a DSP or PC processor or a combination thereof. These systems are targeted at advanced commercial and research applications, which include avionics and military uses. In this category issues of hard real-time specification and code performance are well analysed. The systems developed at this level have immediate end product uses and are not solely used for evaluation purposes. Companies producing solutions at this level include dSPACE [DSPACE2, 5] and Wind River Systems [MATHWORKS4].

#### 1. Medium-End Systems

These systems can be broadly categorised as the PC RTW targets segment and are primarily used in applications with soft real-time specification and for algorithm evaluation purposes. The advantage of these systems is that they can be easily networked and can draw on sophisticated PC visualisation techniques. The systems from Quanser [WINCON1] and TecQuipment [TQ1] are good examples of this category of RTW targets

#### 2. Low-End Systems

At this level barebones systems are incorporated into the RTW. These systems include medium to low-end DSP cards with no real-time OS and network support. These systems have adequate bandwidth for evaluation of simple control algorithms and are simple, cost effective platforms for educational applications. This presents a dilemma to commercial developers, as there is little financial benefit in producing products in this category. This has resulted in academics institution filling this gap and producing in house tools. Example of these develops include the work by Gan [GAN1] and Stylo [STYLO1].

The RADE system is a hybrid of the latter two categories, as it aims to incorporate the benefits of both the PC and DSP platforms:

- The PC will provide network support and visualisation.

- The DSP target will provide real-time code execution.

## 2.5.2 Summary Of Project Goals

- 1. Incorporate maximum RTW version 3 functionality into the RADE framework with the following support:

- Seamless code generation and downloading.

- On-line parameter tuning.

- On-line visualisation within Simulink.

- Full network support

- 2. Document The Mathworks TCP/IP external mode implementation. This will allow for proper understanding of the Mathworks frameworks and facilitate easy version revisions. It will also allow DSP targets to be networked and therefore maximise utilisation of an expensive resource, which makes the RADE system more attractive to teaching applications.

- 3. The development of the RADE framework must conform to an easily maintainable and scaleable framework.

- 4. Apply the RADE framework to the PC32 and ADC64 target DSP cards from Innovative Integration [INNOVATIVE1, 3].

### 2.6. Conclusion

This chapter presented an overview of rapid prototyping and its application to the educational environment. It is clear from the literature that both commercial and academic rapid prototyping tools are finding increasing use in courses to provide students with more interactive laboratory experiments. Theoretical concepts, which are traditionally not easy or practical for students to implement in short laboratory sessions are now, becoming common place in rapid prototyping laboratories. In addition researchers who are not skilled in software engineering can use rapid prototyping tools to implement and evaluate complex applications in real-time.

The Mathworks RTW, which was also featured in this chapter, is being used extensively in engineering education applications. The RTW in conjunction with Simulink provides an effective teaching and research platform that is both scalable and customisable. The open architecture of the RTW allows both commercial and academic rapid prototyping tools to be incorporated and is being well received by students and researchers alike.

While this chapter highlighted uses of the RTW, it did not provide a detailed discussion on the internal workings of Simulink and the RTW. These details are necessary for the implementation of RTW targets and are presented in the next chapter.

# CHAPTER THREE: OVERVIEW OF SIMULINK AND THE RTW

### 3.1. Introduction

This chapter provides an overview of Simulink and the Real Time Workshop, products from The Mathworks, which form the core elements of the RADE system. A large part of the chapter is devoted to RTW conventions, as this information will be required in subsequent chapters. The aim of this chapter is to highlight the important aspects of Simulink and the RTW in the context of work presented in this thesis.

Matlab and Simulink, which form the core products from The Mathworks, are becoming popular tools for modelling and simulation in academic environments [HUGH1]. These products are being widely used in both undergraduate and post-graduate teaching the world over, and are also acquiring a large research user base due to the advanced add-on toolboxes [KOZICK1, GAN1, MATHWORK1]. With the Real Time Workshop add-on extension, Simulink becomes a powerful open architecture, rapid prototyping environment with numerous applications in teaching and research. The RADE system is one such application

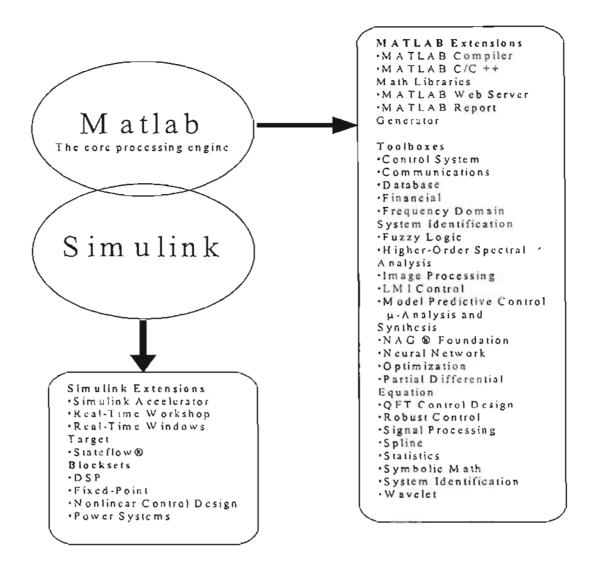

### 3.2. Products Available From The Mathworks

Matlab is the core product from The Mathworks, which is tailored for fast and efficient numerical computation and visualisation. Matlab, which stands for *Matrix Laboratory* is a high performance technical computing and visualisation tool, which provides an easy to use environment were problems and solutions can be expressed in mathematical notation. This product is further enhanced by the availability of numerous advanced application specific toolboxes. The Mathworks also produces a dynamic graphical simulation environment called Simulink, which runs above the core Matlab engine. Simulink is also available with application specific add-on blocksets. Fig. 3.1 shows the entire Mathworks product range and distinguishes Matlab and Simulink components. Matlab and Simulink are well-established software packages, which are being used in both the commercial and academic fields. Its open architecture, which allows for the easy development of customer specific solutions, is a further reason for its wide scale use. Both these packages have become the standard instructional tool for courses in engineering, mathematics and science [MATHWORKS1].

Fig. 3.1: Product range from The Mathworks

The Mathworks provides an extensive set of computing tools with a complete list shown in Fig. 3.1. As shown in Fig. 3.1 The Mathworks extension products, allow Matlab and Simulink functionality to be exported to external programs, by means of the C code or web server applications. There are also two categories of add-on products, toolboxes for Matlab and Blocksets for Simulink. As shown in Fig. 3.1 there are numerous Blocksets and Toolboxes from The Mathworks spanning a wide variety of topics and it is beyond the scope of this thesis to discuss all. Therefore material presented herein will only be that directly relevant to the author's work, of which Simulink and the RTW form a crucial part.

### 3.3. A Overview Of Simulink

### "What is Simulink?

Simulink is a software package for modelling, simulating and analyzing dynamical systems. Its supports linear and non-linear systems, modelled in continuous time, sampled time, or a hybrid of the two. Systems can also be multirate, i.e. have different parts that are sampled or updated at different rates."

Using Simulink Version 3,1999

Simulink forms an integral part of the work presented in this thesis, and it is therefore necessary to review this package to enable the reader to gain an understanding of it. A short overview follows in the next section, using a simple example to illustrate the operation of Simulink. It then focuses on the internal operation of this package, which is necessary to gain a proper understanding of the real-time code generation process.

### 3.3.1 An Example with Simulink

Fig. 3.2: A Simulink simulation

Fig. 3.2 is a Simulink simulation of a simple second order system to a step response and is used to outline the general aspects of a Simulink model. In Fig. 3.2 it is shown that a basic model consists of blocks, an integration solver and a visualisation method. These topics are expanded upon in the following sections

### I. Blocks

Blocks are the elementary components of a Simulink model. There are numerous types of blocks ranging from simple mathematical operations to advanced application specific blocks. Fig. 3.3, shows some of the more common blocks available in the Simulink library [MATHWORKS2].

Fig. 3.3: A sample of the common Simulink library blocks

### II. Libraries

Simulink uses libraries to group common blocks and they have the added advantage of allowing models that contain library blocks, to automatically update when the source blocks are updated. The common Simulink libraries have already been shown in Fig. 3.3

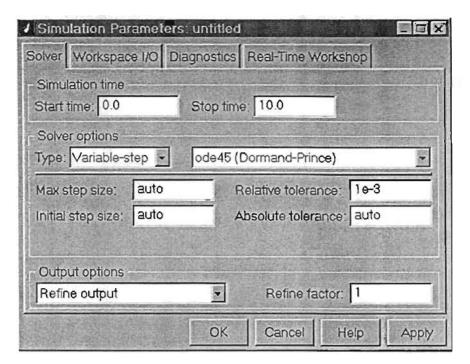

### III. Simulation Parameters

- 1. The Simulink simulation parameters are set in the parameter window, as shown in Fig. 3.4. The import parameters are:

- 2. Start and stop time

These parameters are used to set the duration of a simulation.

3. The integration solver

The solver is a fundamental component of Simulink, which is responsible for the numerical integration of the ordinary differential equations of a model. There are various types of solvers varying from fixed to variable step algorithms [MATHWORK2,3].

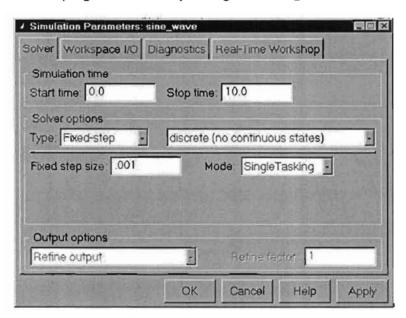

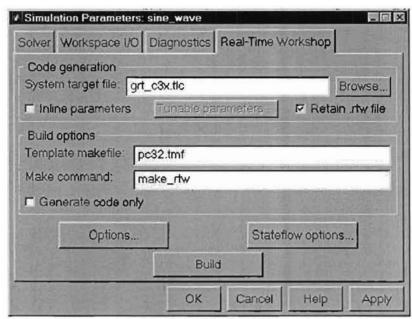

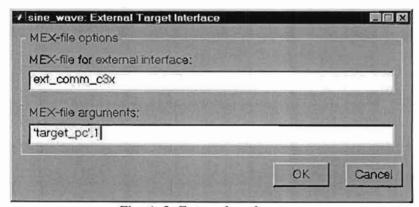

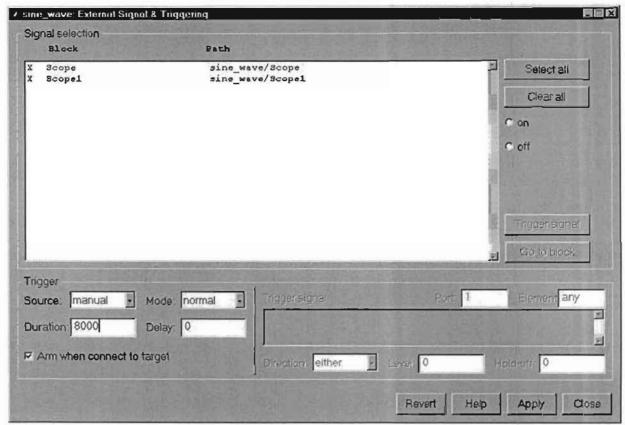

Fig. 3.4: Simulink simulation parameters

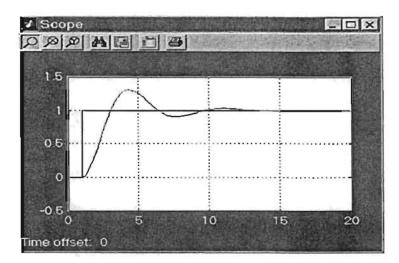

### IV. Visualisation

Visualisation of simulation data is an important aspect of Simulink with which it allows the user to graphically interpret simulation data. There are two methods to view simulation data, firstly to use either a scope or XY graph block and secondly to pass the data to the Matlab workspace and then use one of the, extensive set of, Matlab<sup>1</sup> visualisation functions. Fig. 3.5 is an example of the typical output of a scope block.

Fig. 3.5: The scope block output of the step response of the system in Fig. 3.2

<sup>&</sup>lt;sup>1</sup> Simulink also supports interfacing to the Graphic User Interface (GUI) toolbox, which support the use of advanced animation routines.

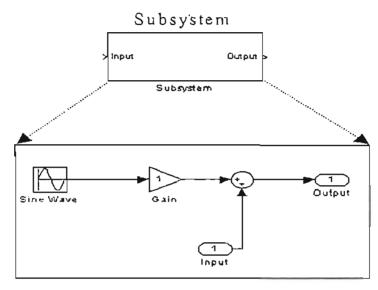

### V. Subsystems and Triggered Subsystems

Subsystems are used in Simulink to build hierarchical models by grouping parts of a model into subsystems<sup>2</sup>. This technique allows models to be constructed in a top-down manner by placing high-level aspects on the first layer and "hiding" model details in lower levels. This makes for easier understanding and navigation of complex Simulink models. Fig. 3.6 details the concept of a subsystem of a simple case.

Contents of subsystem

Fig. 3.6: An example of a subsystem

Fig. 3.7: An example of a triggered subsystem

An event driven subsystem is an extension of this process whereby a subsystem is only executed when triggered by an external trigger source. This technique allows a subsystem within a model to execute in an asynchronous mode, and is used in RTW implementations<sup>3</sup> to synchronise different sections of a model to external signals. Fig. 3.7 shows a triggered

<sup>&</sup>lt;sup>2</sup> A subsystem is a *Virtual Blocks*, these blocks play no active role in a simulation, they are merely a technique to organise a model in a graphically efficient manner.

<sup>&</sup>lt;sup>3</sup> The dSPACE GmbH implementation of the RTW uses this technique [DSPACES]

subsystem.

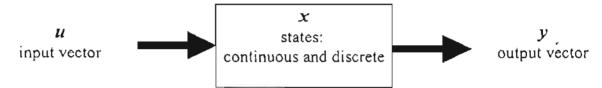

### 3.3.2 How Simulink Works

This section briefly outlines the internal operation of Simulink, which will help with the understanding of how the RTW converts a model into real time code. Every block within a model has the standard characteristic detailed in Fig. 3.8, with the mathematical relationship expressed in equations [3-1], [3-2] and [3-3]. It is evident from these equations that Simulink uses a general state space model to implement dynamical blocks [MATHWORKS2, 3].

Fig. 3.8: General model of a Simulink block [

$$y = f_0(t, x, u)$$

.....(output) [3-1]

$$\dot{x}_c = f_d(t, x, u) \dots \text{(derivative)}$$

[3-2]

$$x_{d_{x-1}} = f_u(t, x, u)$$

....(update for discrete states)

where  $x = x_{continuous} + x_{discrete}$  [3-3]

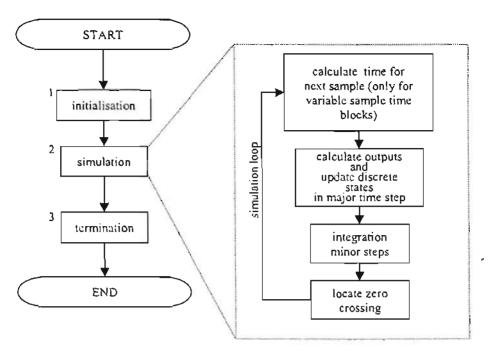

The simulation process is a multistage process that is detailed in Fig. 3.9:

### 1. Initialisation

This step consists of:

- Evaluation of block parameters.

- Reducing model hierarchy to a single tier.

- Sorting blocks for execution order

- Verification of correct signal flow between blocks.

### 2. Simulation stage

The simulation stage involves the repetitive process of finding the state derivative of the model<sup>4</sup> and then integrating it to find the next state value. This process is further enhanced by, integration algorithms, which support variable stepping and zero crossing detection [MATHWORKS2].

### 3. Termination

At this the stage termination routines for the model execute and output data is sent to the workspace.

<sup>&</sup>lt;sup>4</sup> A models state and state derivatives can be evaluated because each block within a model conforms to equations [3-1], [3-2], [3-3].

Fig. 3.9: Flow diagram of Simulink internals

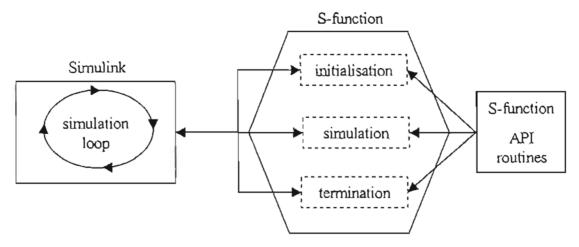

### 3.3.3 An Overview of S-functions

S-functions are a window into Simulink [MATHWORKS3]; they allow third party developers to develop custom blocks for Simulink. It can also be said that all library blocks within Simulink conform to S-function semantics, and therefore understanding S-function allows for a richer understanding of Simulink. This section details the programmatic aspects of S-functions, which has important relevance to the RTW, since custom blocks for the RTW are developed using S-functions and generated code is modelled around S-functions; see section 3.7.3.

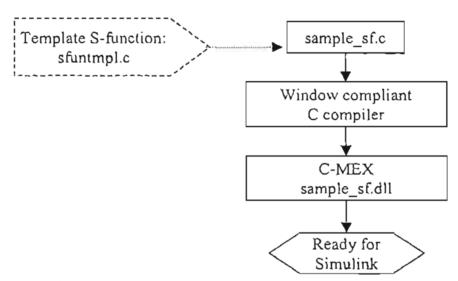

Mathworks provides two techniques for writing a S-function, either using a Matlab script or a C-Matlab Executable (C-MEX). Since only C-MEX files can be used with the RTW, they are discussed exclusively in the following sections.

### I. How S-functions work

An S-function model is uniform for all Simulink blocks, the input to output relationship is shown in Fig. 3.8 and the mathematical model is described in equations [3-1], [3-2], [3-3]. All S-functions export a standard Application Program Interface (API) that Simulink can call into, Fig. 3.10 shows this process. Fig. 3.11 details the step involved in the writing and compiling of a C-MEX S-function. The next section defines The Mathworks conventions for the S-function API.

Fig. 3.10: How Simulink calls into a S-function

Fig. 3.11: The flow diagram of writing and compiling a S-function

### II. The S-function API

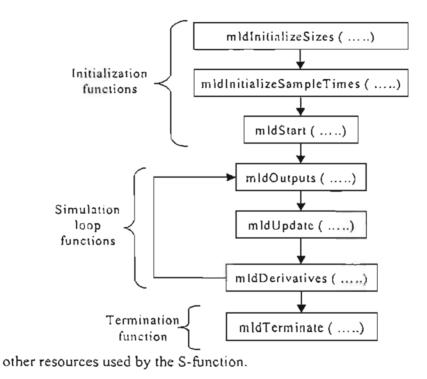

Fig. 3.12 details the function calls for a S-function and their sequence of operation<sup>5</sup>.

### 1. mldInitializeSizes

This is the first function called by Simulink when interfacing to an S-function. It is used to setup block characteristics like, input and output port sizes, number of parameters, block states, working variables and other block functionality.

### 2. mdlInitializeSampleTimes

This function is used to setup the sample times for a S-function.

### 3. mldStart

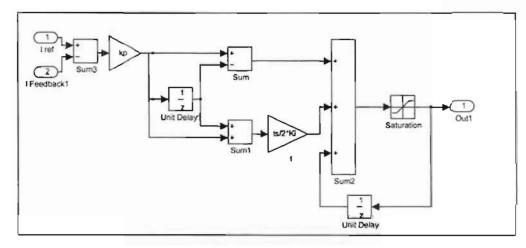

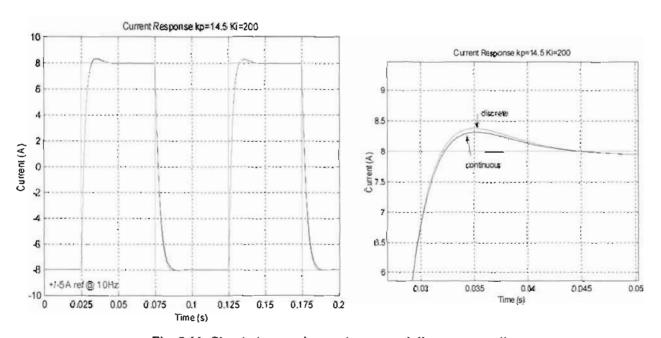

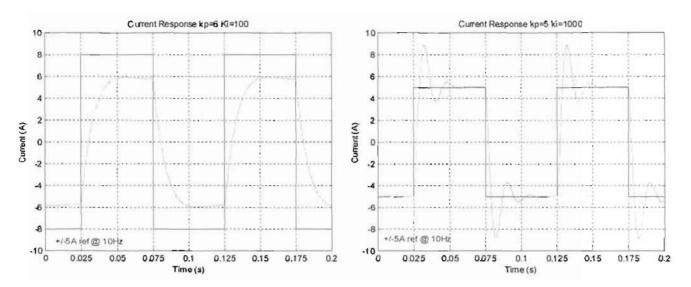

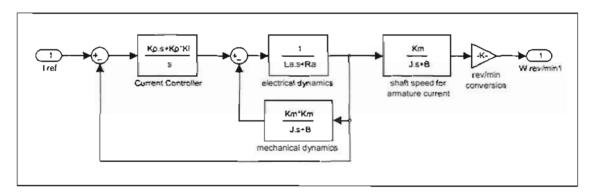

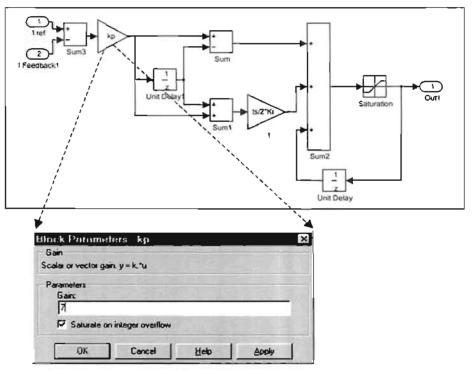

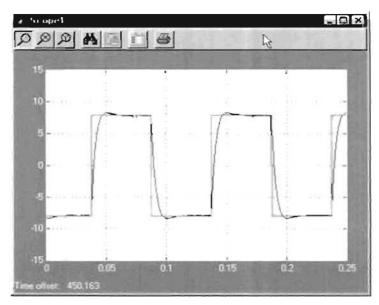

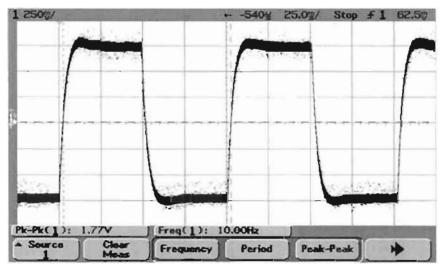

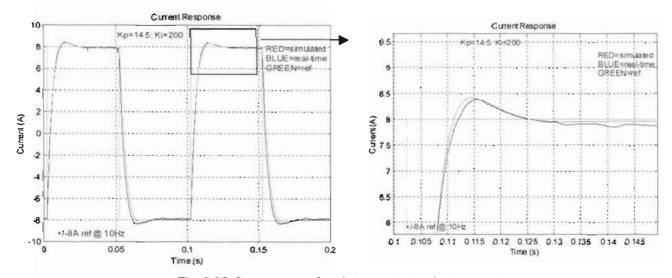

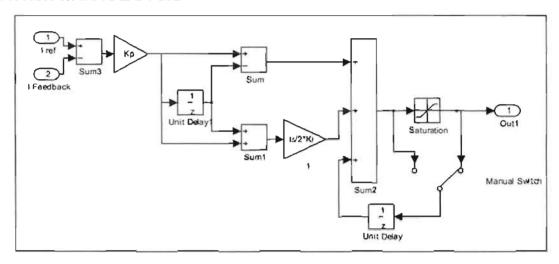

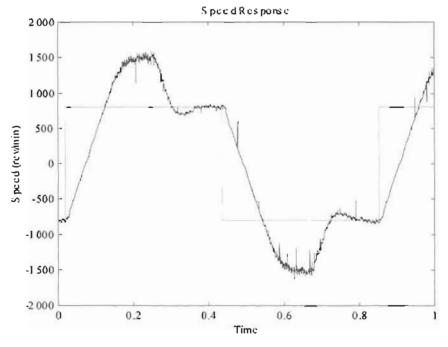

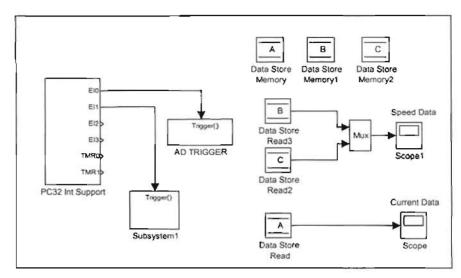

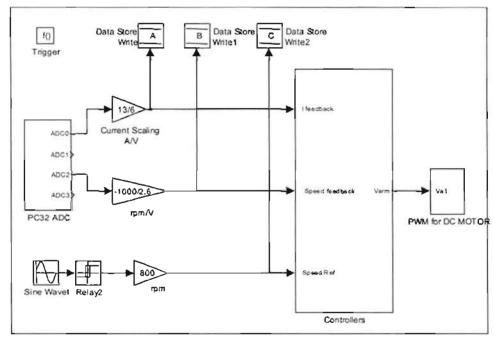

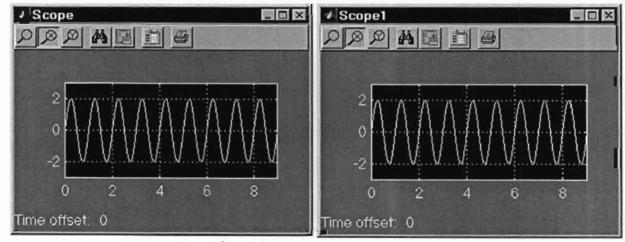

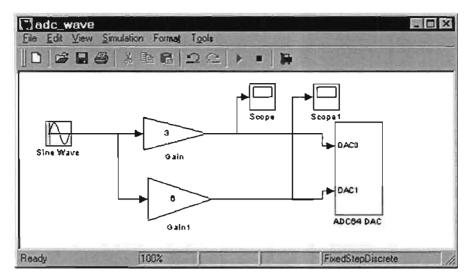

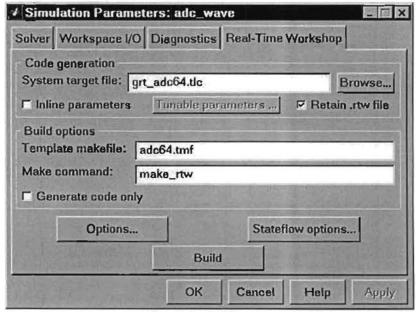

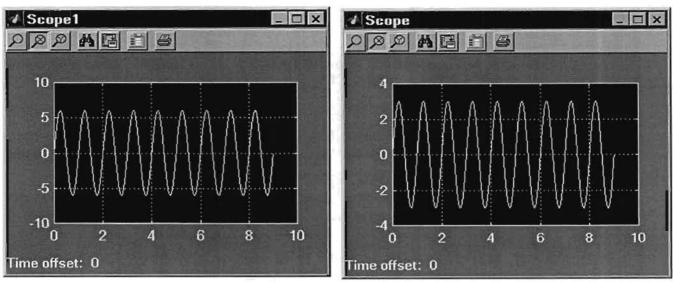

This optional function is called once at the initialisation stage. It can perform any additional application specific initialisation.