# DESIGN EVOLUTION OF DUAL-MATERIAL GATE STRUCTURE IN CYLINDRICAL SURROUNDING DOUBLE-GATE (CSDG) MOSFET USING PHYSICS-BASED ANALYTICAL MODELING

Thesis submitted for the fulfillment of requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

Electronic Engineering

by

ABHA DARGAR

## UNIVERSITY OF KWAZULU-NATAL

INYUVESI YAKWAZULU-NATALI

HOWARD COLLEGE,

COLLEGE OF AGRICULTURE, ENGINEERING AND SCIENCE

UNIVERSITY OF KWAZULU-NATAL, DURBAN - 4041

SOUTH AFRICA.

STUDENT NO.: 218087138 APRIL 2021

## **DESIGN EVOLUTION OF DUAL-MATERIAL GATE** STRUCTURE IN CYLINDRICAL SURROUNDING **DOUBLE-GATE (CSDG) MOSFET USING** PHYSICS-BASED ANALYTICAL MODELING

| Student:                                   | Supervisor:                          |

|--------------------------------------------|--------------------------------------|

| Abha Dargar                                | Prof. (Dr.) Viranjay M. Srivastava   |

|                                            |                                      |

|                                            |                                      |

| This thesis submitted                      | in fulfillment of the requirements   |

| for the degree of Doctor o                 | f Philosophy: Electronic Engineering |

|                                            | in                                   |

| Howard College of Ag                       | riculture, Engineering & Science     |

| University of                              | KwaZulu-Natal, Durban                |

| S                                          | outh Africa.                         |

|                                            |                                      |

|                                            |                                      |

|                                            |                                      |

| As the candidate's supervisor, I have appr | roved this thesis for submission.    |

| Signed                                     | Date: 13 April 2021                  |

Name: Prof. (Dr.) Viranjay M. Srivastava

#### **DECLARATION 1 – PLAGIARISM**

I, ABHA DARGAR with Student Number 218087138 with the thesis entitled "DESIGN EVOLUTION OF DUAL-MATERIAL GATE STRUCTURE IN CYLINDRICAL SURROUNDING DOUBLE-GATE MOSFET USING PHYSICS-BASED ANALYTICAL MODELING"

hereby solely declare that:

- (i) The research reported in this thesis, except where otherwise indicated, is my original research work.

- (ii) This thesis has not been submitted for any degree or examination at any other university.

- (iii) This thesis does not contain other person's data, pictures, graphs or other information unless specifically acknowledged as being sourced from other persons.

- (iv) This thesis does not contain other person's writing unless specifically acknowledged as being sourced from other researchers. Where other written sources have been quoted, then:

- a. Their words have been re-written but the general information attributed to them has been referenced;

- b. Where their exact words have been used, then their writing has been placed inside quotation marks and referenced.

- (v) Where I have reproduced a publication of which I am an author, co-author or editor, I have indicated in detail which part of the publication was actually written by myself alone and have fully referenced such publications.

- (vi) This thesis does not contain text, graphics or tables copied and pasted from the Internet, unless specifically acknowledged, and the source being detailed in the thesis and in the references sections.

ABHA DARGAR Date: 13 April 2021

i

#### **DECLARATION 2 - PUBLICATIONS**

DETAILS OF CONTRIBUTION TO PUBLICATIONS that form part and/or include research presented in this thesis (include publications that have been submitted, *in the press* and published and give details of the contributions of each author to the experimental work and writing of each publication).

#### JOURNAL PUBLICATIONS

- Abha Dargar and Viranjay M. Srivastava, "Thickness Modeling of Short-Channel Cylindrical Surrounding Double-Gate MOSFET at Strong Inversion using Depletion Depth Analysis," *Micro and Nanosystems*, vol. 13, no. 3, pp. 319-325, 2021. (Included in Chapter 6). [DoHET, Scopus]

- 2. Abha Dargar and Viranjay M. Srivastava, "Analytical Modeling of Dual-Material Gate Structure in Cylindrical Surrounding Double-Gate MOSFET," *Journal of Computational Electronics*, under review, March 2021 (Included in Chapter 7).

[DoHET, Scopus]

- 3. Abha Dargar and Viranjay M. Srivastava, "Performance Comparison of Gate-Metal Engineered Cylindrical Surrounding Double-gate MOSFET," *International Journal of Electronics and Telecommunication*, vol. 67, no. 1, pp. 29-34, January 2021.

(Included in Chapter 7).

[DoHET, Scopus]

- **4. Abha Dargar** and Viranjay M. Srivastava, "Cylindrical Surrounding Double-Gate MOSFET and Orientation of Dual-Material Gate- a Review," *Journal of Engineering Science and Technology Review*, under review, Feb. 2021 (**Included in Chapter 2 and Chapter 8**).

[DoHET, Scopus]

#### **CONFERENCES PUBLICATIONS**

**5. Abha Dargar** and Viranjay M. Srivastava, "Capacitive Model of CSDG MOSFET at Pinch-off for Switching Characteristics," *IEEE 10<sup>th</sup> International Conference on Computing, Communication and Networking Technologies (ICCNT-2019)*, Kanpur, India, 6-8 July 2019, pp. 1-4. (**Included in Chapter 3**). [**IEEE**]

- **6. Abha Dargar** and Viranjay M. Srivastava, "Analysis of Electrical Field in Uniformly Doped Cylindrical Surrounding Double-Gate MOSFET," *IEEE 10<sup>th</sup> International Conference on Computing, Communication and Networking Technologies (ICCNT-2019)*, Kanpur, India, 6-8 July 2019, pp. 1-4. (**Included in Chapter 4**). **[IEEE]**

- 7. Abha Dargar and Viranjay M. Srivastava, "Performance Improvement of CSDG MOSFET with Dual-metal Gate Technique," presented and abstracted (poster session) in *Postgraduate Research and Innovation Symposium (PRIS- 2019)*, University of KwaZulu-Natal, Durban, South Africa, 17 October 2019. (Included in Chapter 7). [Best Poster Award Winner]

- **8. Abha Dargar**, Shashi K. Dargar and Viranjay M. Srivastava, "Influence of Gate-Dielectric Material and Thickness Variation on the Depletion Width of MOSFET Device," 7<sup>th</sup> International Mathematics-Engineering-Science and Health Sciences Congress (IMES-HSC 2019), Rome, Italy, 14-16 June 2019, pp. 1-4. (Included in Chapter 5).

- **9. Abha Dargar,** Shashi K. Dargar, and Viranjay M. Srivastava, "Effect of Gate-Underlap Lengths in High-k Dielectric Based Silicon-Nanowire Gate-All-Around TFET," *7<sup>th</sup> International Mathematics-Engineering-Science and Health Sciences Congress*, Rome, Italy, pp. 18-21, 14-16 June 2019. (**Included in Chapter 5**)

- **10. Abha Dargar,** Shashi K. Dargar, and Viranjay M. Srivastava, "Comparative Analysis of Single and Double-Gate Amorphous-IGZO Thin-Film Transistors," 7<sup>th</sup> *International Mathematics-Engineering-Science and Health Sciences Congress*, Rome, Italy, pp. 5-10, 14-16 June 2019.

#### **PREFACE**

The research work in this thesis was implemented by Abha Dargar, under the supervision of Prof. (Dr.) Viranjay M. Srivastava at the Discipline of Electrical, Electronic and Computer Engineering, Howard College, University of KwaZulu-Natal, Durban, South Africa.

The content of research outcome included in chapter 3 to chapter 6 of this thesis have been published in the form of a research article in the Journals including Micro and Nano Systems, full-text proceeding in IEEE Xplore digital library, and the remaining in chapter 7 have been submitted to the consideration of publication.

This thesis's content in chapters 3 and 4 have been presented in the 10<sup>th</sup> International Conference on Computing, Communication, and Networking Technologies (ICCNT-2019), held in India.

This thesis's content in chapter 5 has been presented in the 7<sup>th</sup> International Mathematics-Engineering-Science and Health Sciences Congress (IMES-HSC 2019) held in Italy.

This thesis's partial content of chapter 7 has been presented in the symposium titled Postgraduate Research and Innovation Symposium (PRIS- 2019) held in the University of KwaZulu-Natal, South Africa.

**ACKNOWLEDGMENTS**

Foremost, I would like to express my sincere gratitude to my Ph. D. Supervisor Prof.

(Dr.) Viranjay M. Srivastava, for his invaluable guidance, encouragement, endless

support, and interest during this research. His support helped in all the time of research

and writing of this thesis. I could not have imagined having a better advisor and mentor

for my research and Ph. D. studies. I sincerely appreciate his willingness to discuss

research related problems as often as needed. I am grateful to him for holding me to a

research standard and taught me how to do research. He has been an inspiration.

I want to devote special thanks to all the academic staff and my research co-colleagues

of the department of electronic engineering at Howard College, University of KwaZulu-

Natal, Durban, South Africa, who contributed directly or indirectly to the improvement of

my research work from their advice, support, and encouragements.

I bow my head in all my humility for the blessings of my parents Dr. Om Prakash

Nyati and Mrs. Manju Nyati, my loving in-law's parents, Mr. Mahaveer Prasad Dargar

and Mrs. Basanti Devi Dargar, who stood as a source of light, always inspiring me to

achieve. I shall forever remain indebted for their unconditional love and blessing, which

they always shower on me.

I deeply admire my brother Mr. Manoj Nyati, Dr. Ravikant Dargar, and loving sister

Dr. Aradhana for their love and support.

I express my thanks and sincere gratitude to my husband, Dr. Shashi Kant Dargar, and

my daughter Maithilee Dargar for their untiring support and love.

Last but not least, I am highly thankful and admire the grace of almighty God, who

bestowed and showered his kindness to all humankind.

ABHA DARGAR

218087138

V

#### **ABSTRACT**

The Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is the fundamental component in present Micro and Nano-electronics device applications, such as switching, memory devices, communication devices, etc. MOSFET's dimension has shrunk down following Moore's law to attain high-speed operation and packing density integration. The scaling of conventional MOSFET has been the most prominent technological challenge in the past few years because the decreasing device dimensions increase the charge sharing from the source to the drain and that in turn give rises to the reduced gate-control over the channel, hot carrier induced degradation, and other SCEs. These undesired effects devaluate the device performance that compels optimum device design analysis for particular operating conditions.

Therefore, several innovative device design/architectures, including Double-gate, FinFET, Surrounding gate MOSFET, etc., have been developed to mitigate device scaling challenges. Comprehensive research can be traced long for one such promising gate-all-around MOSFET, i.e., Cylindrical Surrounding Double-Gate (CSDG) MOSFET centrally hollow concentric structure, provides an additional internal control gate that improves the device electrical performance and offers easy accessibility. There have been several developments in terms of improvements, and applications of CSDG MOSFET have been practiced since after its evolution.

This thesis's work has been targeted to incorporate the gate material engineering in the CSDG structure after appropriate analysis of device physics-based modeling. In particular to the proposed structure, the electric field, pinch off capacitance, and after that thickness of the device parameters' dependence have been mathematically derived from attaining the objective. Finally, a model based on a dual-material gate in CSDG MOSFET has been proposed. The electrical field in CSDG MOSFET has been analyzed in detail using a mathematical derivation of device physics, including the Surface-Potential, threshold voltage, and the gate-oxide capacitances of the internal and external part of the device. Further, the gate-oxide capacitance of CSDG MOSFET, particularly to the device pinch-off condition, has been derived. Since the device operation and analysis at the shorter channel are not similar to conventional long-channel MOSFETs, the depletion-width variation has been studied.

The identified notion has been applied to derive the approximate numerical solution and silicon thickness inducing parameters for CSDG MOSFET to deploy the improvements in the device performance and novel design modifications. As the gatematerial and gate-stack engineering is an alternative to overcome the device performance degradation by enhancing the charge transport efficiency, the CSDG MOSFET in a novel Dual-Metal Gate (DMG) structure design has been proposed and analyzed using the solution of 2D Poisson's equations in the geometrical boundary conditions of the device. The model expressions obtained solution using the proposed structure has been compared with a single metal gate structure.

Finally, it has been analyzed that the proposed model exhibits an excellent match with the analytical model. The obtained DMG device structure advances the carrier velocity and transport efficiency, resulting in the surface-potential profile caused by dissimilar gate metal work-function. The superior device characteristics obtained employing a dual-material structure in CSDG are promising and can reduce the threshold voltage roll-off, suppress the hot-carrier effects and SCEs.

## TABLE OF CONTENTS

| DECLARATION 1 – PLAGIARISM                                          | i    |

|---------------------------------------------------------------------|------|

| DECLARATION 2 - PUBLICATIONS                                        | ii   |

| PREFACE                                                             | iii  |

| ACKNOWLEDGMENTS                                                     | iv   |

| ABSTRACT                                                            | viii |

| Table of Contents                                                   | 1    |

| List of Figures                                                     | 4    |

| List of Tables                                                      | 7    |

| List of Symbols                                                     | 8    |

| List of Abbreviations                                               | 10   |

| CHAPTER -1 INTRODUCTION                                             | 11   |

| 1.1. MOSFET Overview                                                | 11   |

| 1.2. Operation Mechanism of a MOSFET                                | 12   |

| 1.2.1. Metal-Oxide-Semiconductor Structure                          | 12   |

| 1.2.2. MOSFET Structure and Channel Formation                       | 13   |

| 1.3. Scaling of Transistor                                          | 15   |

| 1.3.1. Benefits of Scaling                                          | 18   |

| 1.3.2. Types of Scaling                                             | 19   |

| 1.3.3. Scaling Challenges                                           | 21   |

| 1.4. Short-Channel Effects (SCEs)                                   | 21   |

| 1.4.1. Two-Dimensional Field Profile ( $V_{TH}$ Reduction and DIBL) | 22   |

| 1.4.2. Very High Electric Field Strength (Impact Ionization)        | 24   |

| 1.4.3. Mobility Degradation and Carrier Velocity Saturation.        | 24   |

| 1.4.4. Channel Length Modulation (CLM) and Punch-Through            | 26   |

| 1.5. Background and Evolution of CSDG MOSFET                        | 28   |

| 1.6. Device Compact and Analytical Modeling                         | 30   |

| 1.7. Objective of the Research Work                                 | 31   |

| 1.8. Research Questions                                             | 31   |

| 1.9. Research Contribution of this Thesis                           | 34   |

| 1.10. | Organization of the Thesis                               | 34 |

|-------|----------------------------------------------------------|----|

| СНА   | PTER -2 REVIEW OF LITERATURES                            | 36 |

| 2.1.  | Review of Analytical Models Developments                 | 36 |

| 2.2.  | Review of Progress in Gate-Capacitance Analysis          | 39 |

| 2.3.  | Research Progress in CSDG MOSFET                         | 39 |

| 2.4.  | Review of Gate Material Engineering                      | 40 |

| 2.5.  | Motivation                                               | 42 |

| СНА   | PTER-3 CAPACITANCE ANALYSIS OF CSDG MOSFET AT PINCH-OFF  | 44 |

| 3.1.  | Gate-capacitance in CSDG MOSFET                          | 44 |

| 3.2.  | Analysis of Oxide Capacitance                            | 46 |

| 3.3.  | Oxide Capacitance of the Internal Gate                   | 47 |

| 3.4.  | Oxide Capacitance of the External Gate                   | 48 |

| 3.5.  | Chapter Summary                                          | 51 |

| СНА   | PTER-4 ELECTRICAL FIELD ANALYSIS IN CSDG MOSFET          | 52 |

| 4.1.  | Electric Field in CSDG Due to Oxide Capacitances         | 52 |

| 4.2.  | Theory of Electric Field in CSDG MOSFET                  | 54 |

| 4.3.  | Derivation of the Electric Field Analysis in CSDG MOSFET | 54 |

| 4.4.  | Results Analysis                                         | 58 |

| 4.5.  | Chapter Summary                                          | 59 |

| СНА   | PTER-5 ANALYSIS OF DEPLETION WIDTH IN MOSFET             | 61 |

| 5.1.  | Introduction                                             | 61 |

| 5.2.  | Depletion width in MOSFET                                | 63 |

| 5.3.  | Modeling and Analysis                                    | 65 |

| 5.4.  | Chapter Summary                                          | 67 |

| СНА   | PTER-6 THICKNESS ANALYSIS OF CSDG MOSFET                 | 68 |

| 6.1.  | Introduction                                             | 68 |

| 6.2.  | Depletion Depth in CSDG MOSFET                           | 69 |

| 6.3.  | Evolution of Depletion depth in MOSFET                   | 70 |

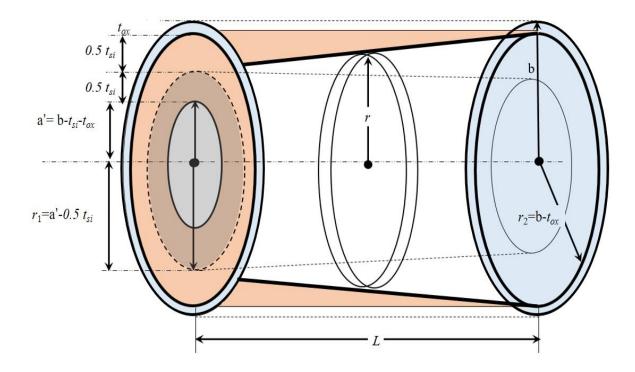

| 6.4.  | Optimum Semiconductor Thickness at Strong Inversion      | 72 |

| 6.5.   | Optimum Semiconductor Thickness at $V_{\rm GS} > V_{\rm TH}$ | 73  |

|--------|--------------------------------------------------------------|-----|

| 6.6.   | Result and Analysis                                          | 76  |

| 6.7.   | Chapter Summary                                              | 81  |

| CHA    | PTER-7 DUAL-METAL GATE STRUCTURE IN CSDG MOSFET              | 83  |

| 7.1.   | Conception of CSDG MOSFET with Dual-Metal Gate               | 83  |

| 7.2.1. | Two-Dimensional Model for Surface-Potential                  | 88  |

| 7.2.2. | Gate Charge and Threshold Voltage Model                      | 94  |

| 7.3.   | Model Framework of Device Simulation                         | 95  |

| 7.4.   | Results and Discussion                                       | 98  |

| 7.4.   | Chapter Summary                                              | 104 |

| CHA    | PTER-8 CONCLUSIONS AND FUTURE RECOMMENDATIONS                | 106 |

| 8.1.   | Conclusions                                                  | 106 |

| 8.2.   | Future Recommendations                                       | 108 |

| REFE   | ERENCES                                                      | 110 |

| APPE   | ENDIX                                                        | 128 |

## **List of Figures**

| Fig. 1.1.  | Structure of a conventional MOSFET.                                                                                                | 12 |

|------------|------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 1.2.  | Channel formation in n-channel MOSFET.                                                                                             | 14 |

| Fig. 1.3.  | Visualization of Moore's Law (a) microchip transistor size (b) the transistors'numbers commercially integrated into the processor. | 16 |

| Fig. 1.4.  | Number of transistors and gate-length reduction over the years.                                                                    | 17 |

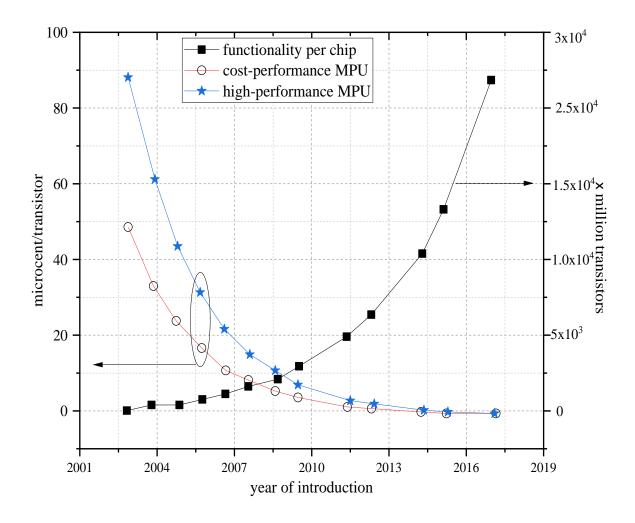

| Fig. 1.5.  | Performance of high-speed Microprocessor unit and the functionality versus the year of technology nodes.                           | 18 |

| Fig. 1.6.  | Sketch of MOSFET scaling.                                                                                                          | 19 |

| Fig. 1.7.  | Effect of channel length reduction on threshold voltage.                                                                           | 22 |

| Fig. 1.8.  | DIBL (a) illustration of the effect, (b) effect on the current characteristics.                                                    | 23 |

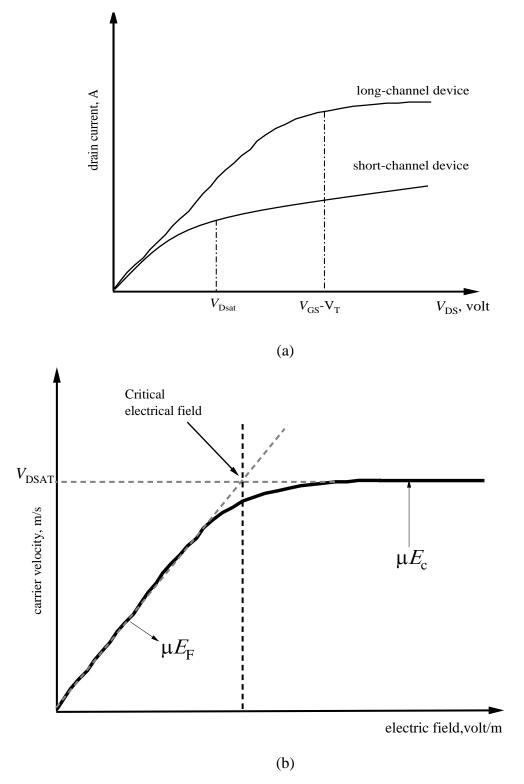

| Fig. 1.9.  | Velocity saturation in short-channel device (a) nonlinear operation, (b) critical electric field.                                  | 25 |

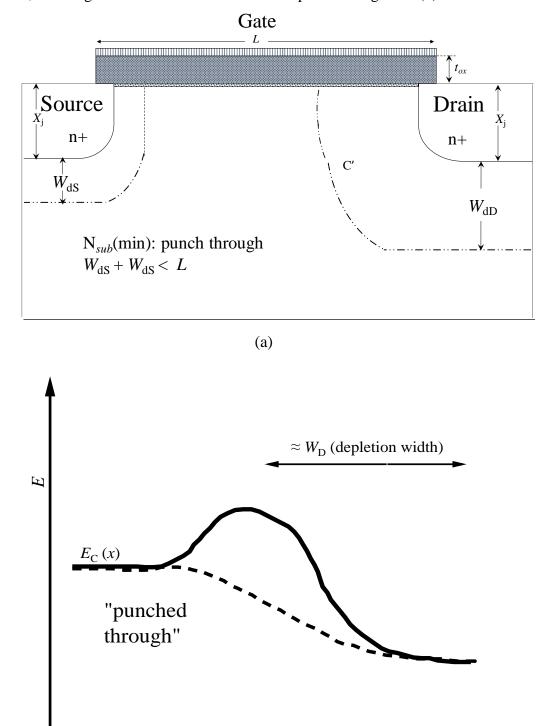

| Fig. 1.10  | . (a) Representation of Channel length Modution and (b) punch-through condition in short-channel MOSFET.                           | 27 |

| Fig. 1. 11 | Multigate and surrounding gate MOSFET structures.                                                                                  | 28 |

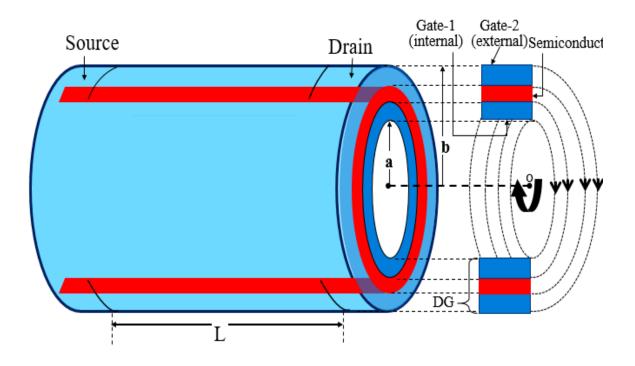

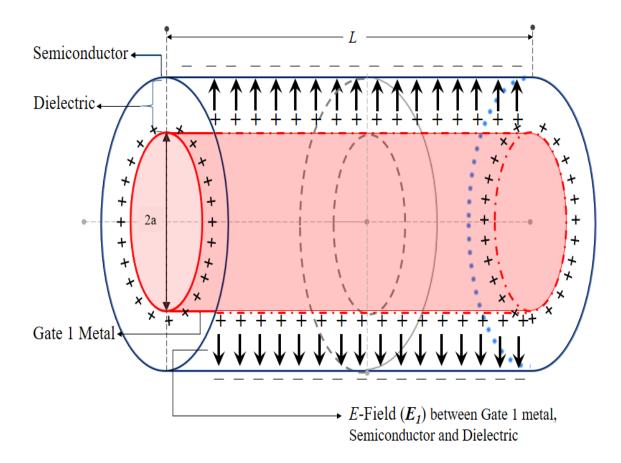

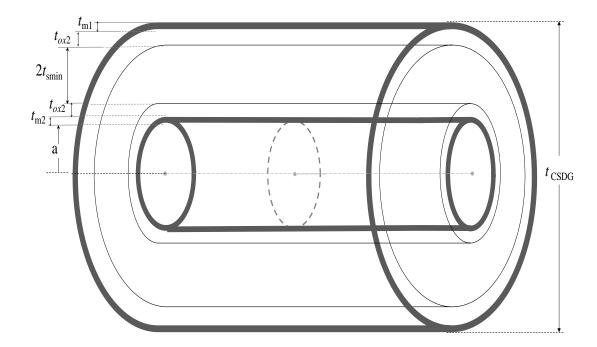

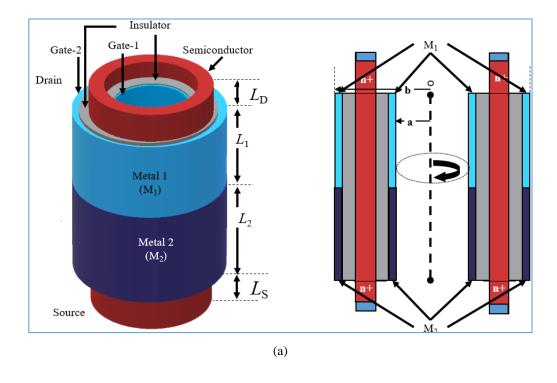

| Fig. 1. 12 | 2. (a) Schematic of Cylindrical Surrounding Double-Gate (CSDG) MOSFET structure.                                                   | 29 |

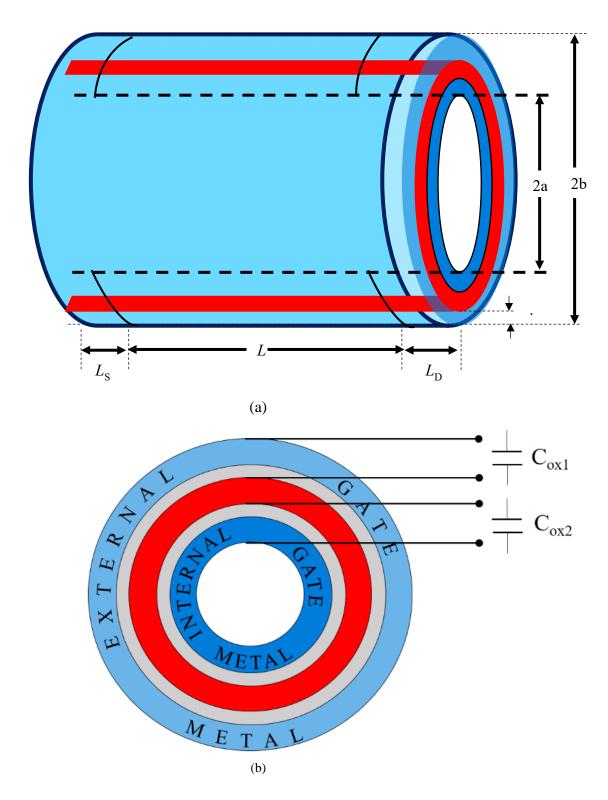

| Fig. 3.1.  | The geometry of (a) a CSDG structure, and (b) representation of oxide capacitance in CSDG MOSFET.                                  | 45 |

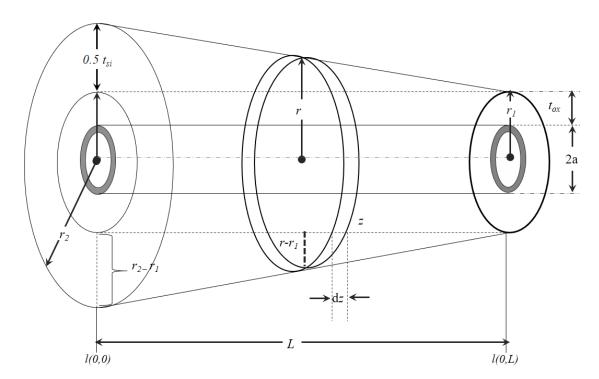

| Fig. 3.2.  | Calculation of internal gate-oxide capacitance at pinch-off.                                                                       | 46 |

| Fig. 3.3.  | Calculation of external gate-oxide capacitance at pinch-off.                                                                       | 49 |

| Fig. 4.1. | Illustration of CSDG structure (a) oxide-capacitances and (b) surface and the field charges.                              | 53 |

|-----------|---------------------------------------------------------------------------------------------------------------------------|----|

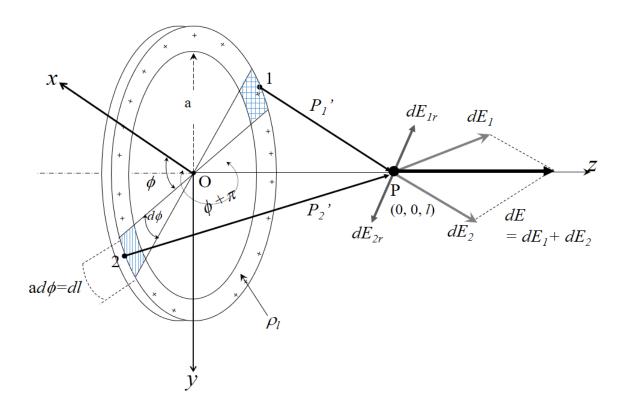

| Fig. 4.2. | Schematic of cylindrical metal-oxide-semiconductor structure.                                                             | 55 |

| Fig. 4.3. | Electric field due to uniformly charged ring for calculating electric field along the length.                             | 56 |

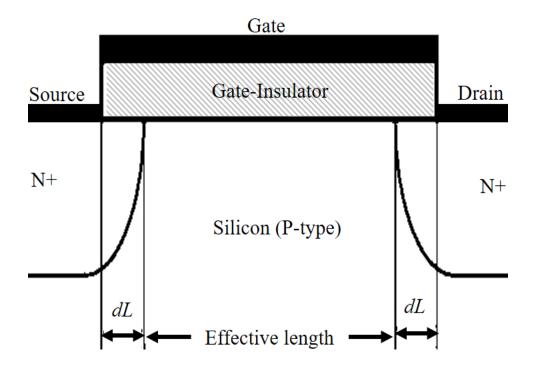

| Fig. 5.1. | A typical Short channel-MOSFET.                                                                                           | 61 |

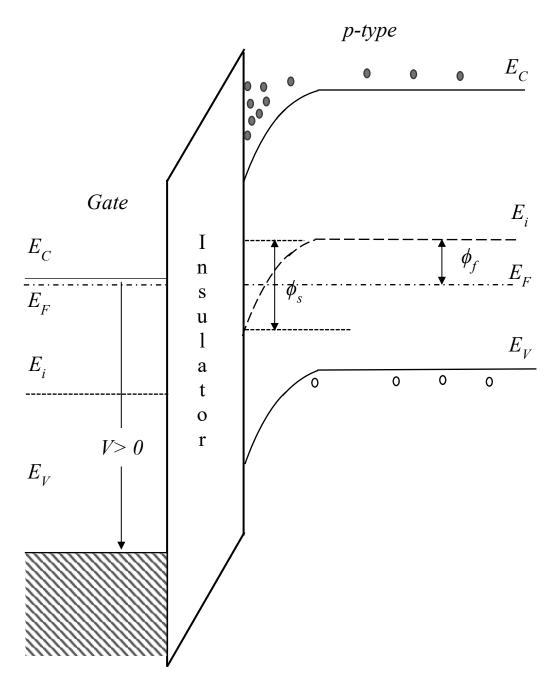

| Fig. 5.2. | Energy band of MOSFET at depletion.                                                                                       | 62 |

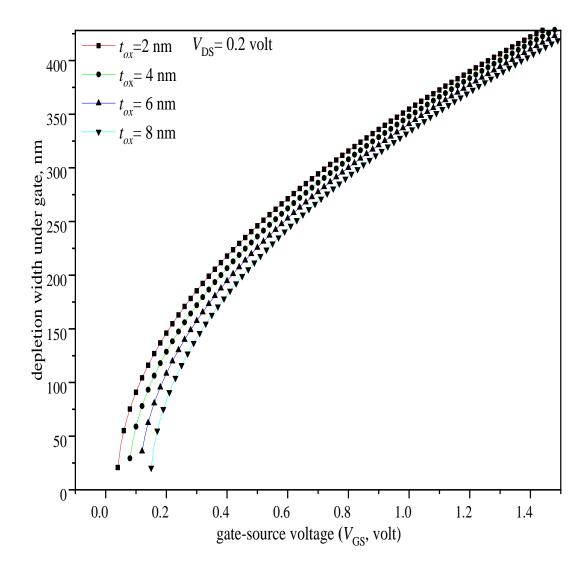

| Fig. 5.3. | Gate-oxide thickness effect on Depletion width.                                                                           | 63 |

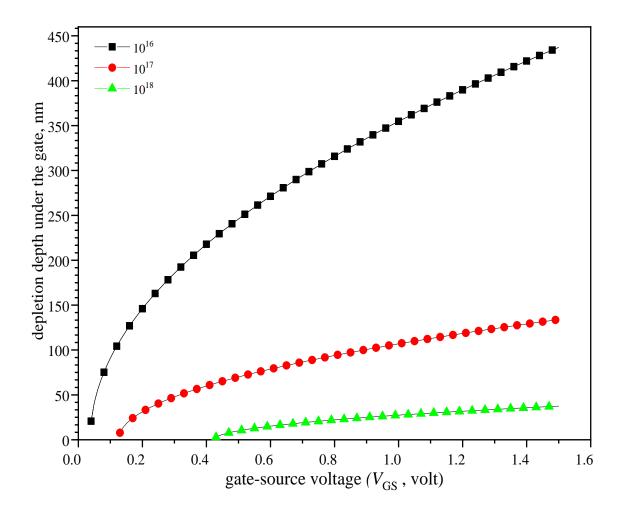

| Fig. 5.4. | Effect of variation in doping on depletion depth of the device.                                                           | 64 |

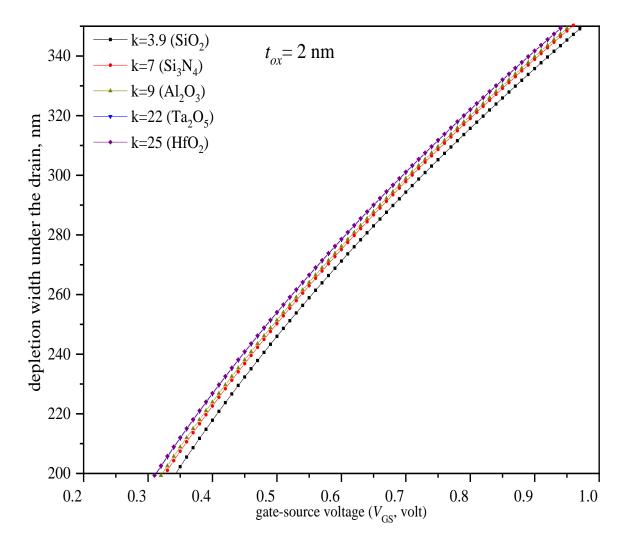

| Fig. 5.5. | Oxide materials effects on depletion width.                                                                               | 66 |

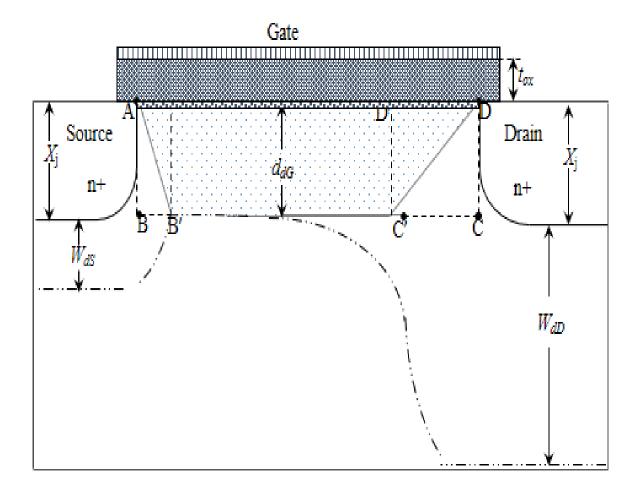

| Fig. 6.1. | Induced depletion regions in MOSFET.                                                                                      | 69 |

| Fig. 6.2. | Energy band of MOSFET at inversion.                                                                                       | 70 |

| Fig. 6.3. | Schematic representation of thickness at strong inversion in CSDG MOSFET structure.                                       | 75 |

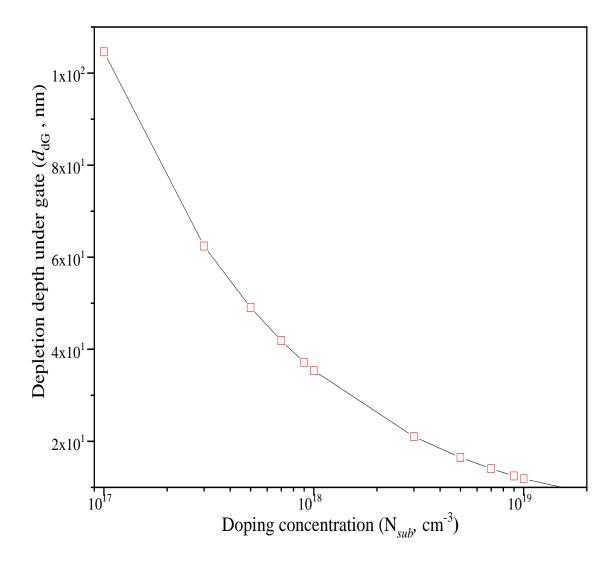

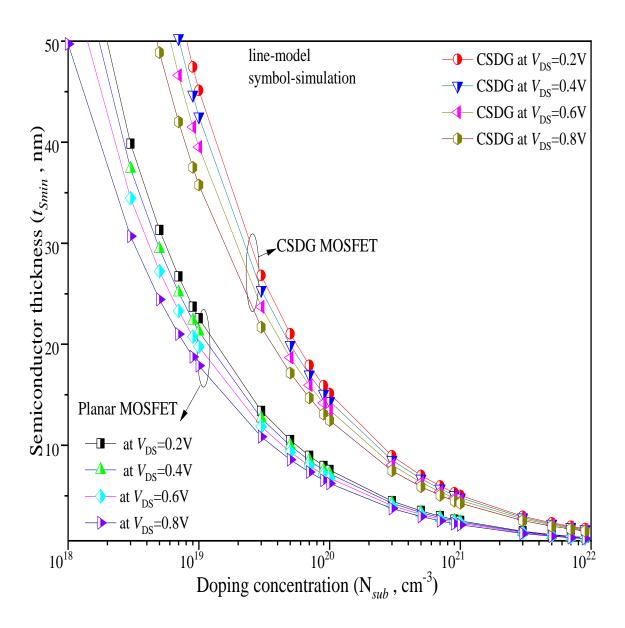

| Fig. 6.4. | Depletion depth under gate versus doping concentration at $\phi_s$ =2 $\phi_f$ .                                          | 75 |

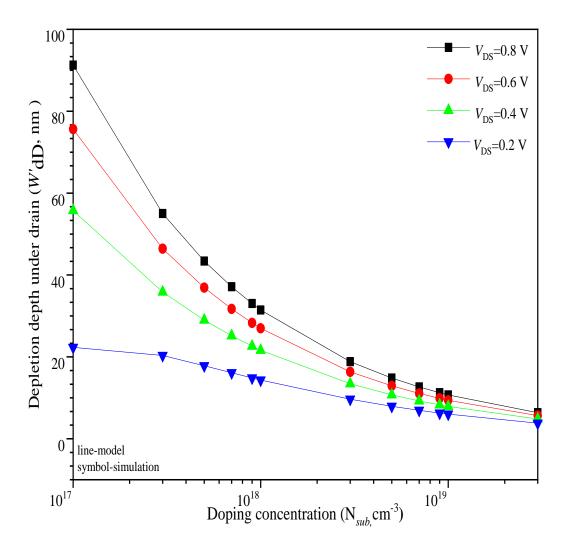

| Fig. 6.5. | Depletion width under the drain versus doping concentration at various $V_{\rm DS}$ .                                     | 79 |

| Fig. 6.6. | Comparison of semiconductor thickness versus doping concentration in planar and CSDG structures at various $V_{\rm DS}$ . | 80 |

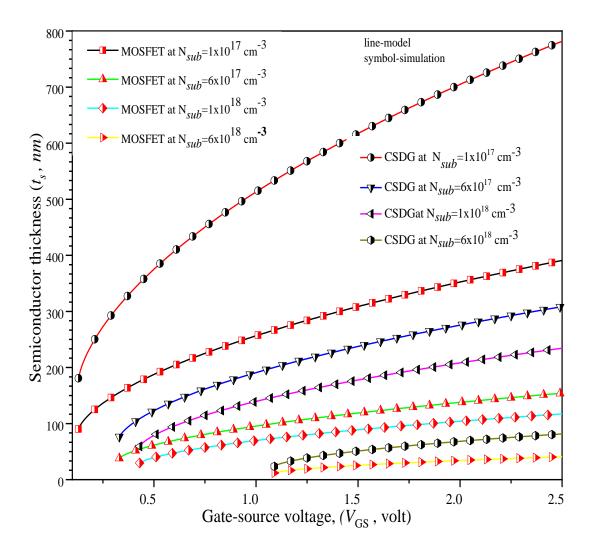

| Fig. 6.7. | CSDG Silicon thickness variation with applied Gate voltage at various $N_{sub}$ and $V_{DS}$ =0.2.                        | 81 |

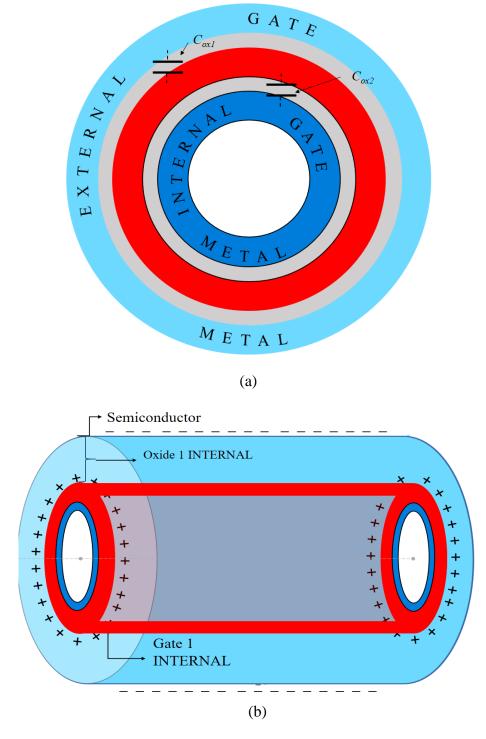

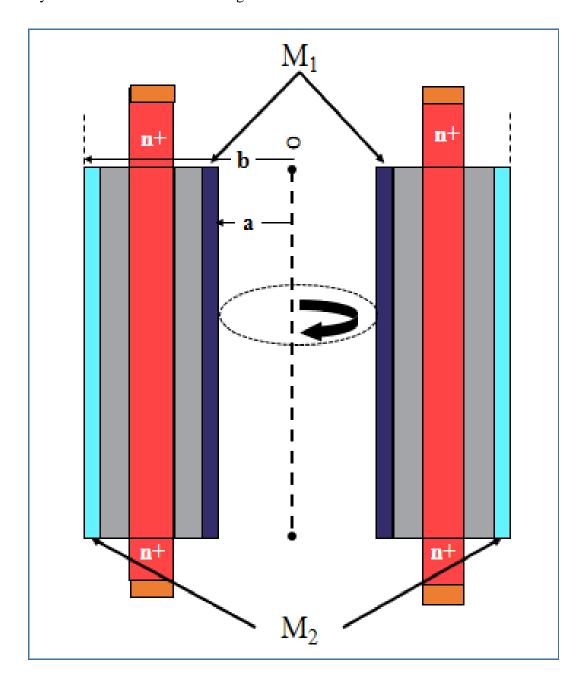

| Fig. 7.1. | Proposed schematic of cylindrical DMG architecture of CSDG MOSFET.                                                        | 84 |

| Fig. 7.2. | Cylindrical DMG architecture of two-dimension cross-sectional view.                                                       | 85 |

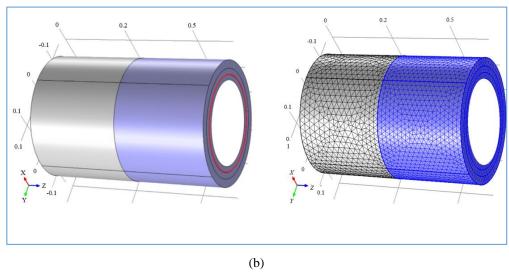

| Fig. 7.3.  | A stacked-dual-metal gate based CSDG MOSFET device (a) schematic and a cross-sectional view, (b) simulation and meshing structure.         | 86  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

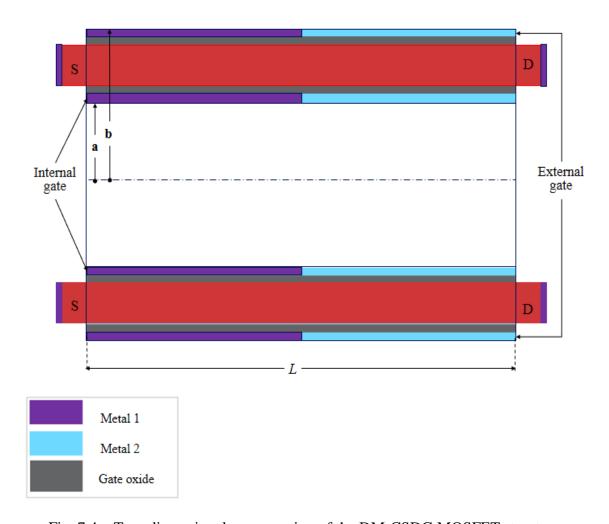

| Fig. 7.4.  | Two-dimensional cross-section of the DM-CSDG MOSFET structure.                                                                             | 87  |

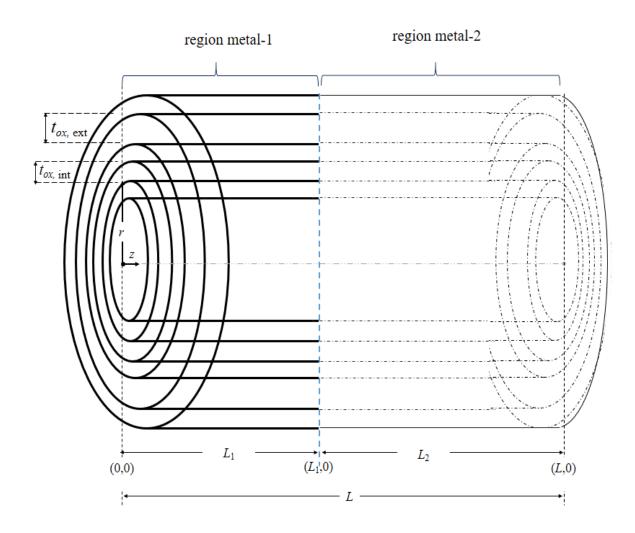

| Fig. 7.5.  | DM-CSDG MOSFET structure outlining the two metal regions.                                                                                  | 88  |

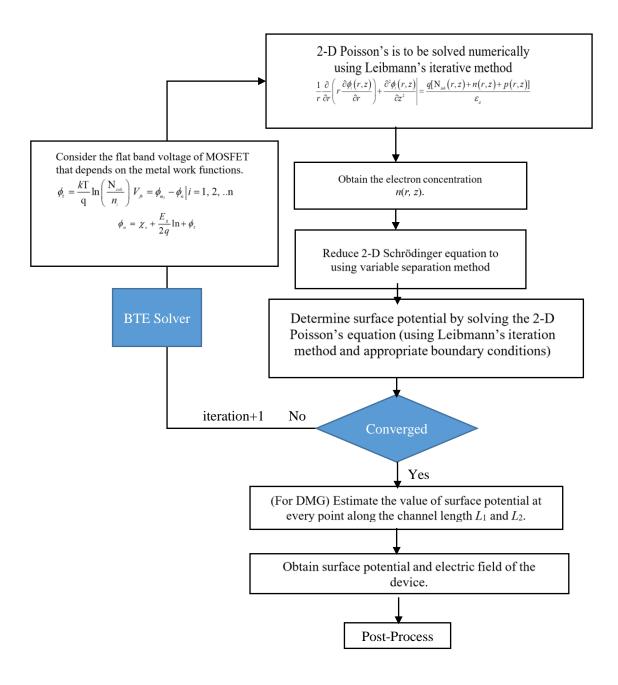

| Fig. 7.6.  | Model framework for the estimation of surface-potential.                                                                                   | 96  |

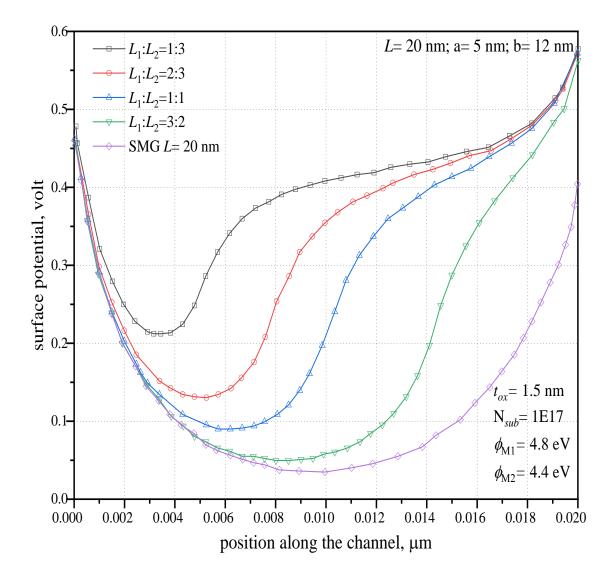

| Fig. 7.7.  | Surface-potential profile versus position along the channel in stacked DMG-CSDG device at varied region lengths.                           | 98  |

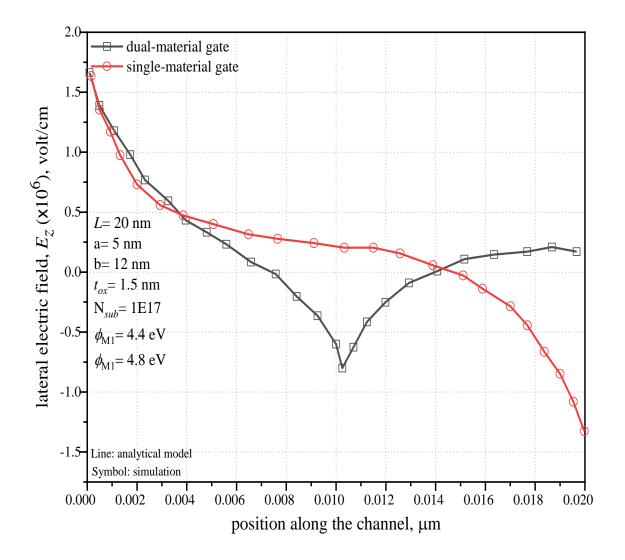

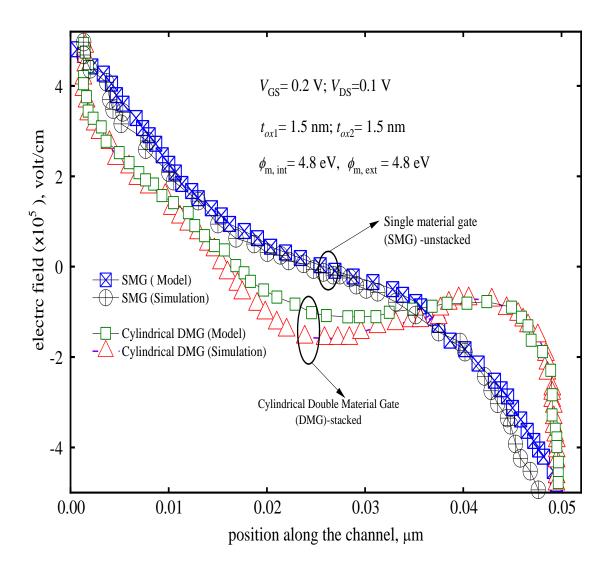

| Fig. 7.8.  | Comparison of electric field profile in dual-metal and single metal gate structures of CSDG MOSFET at $L$ =20 nm, a=5 nm, b=12 nm.         | 99  |

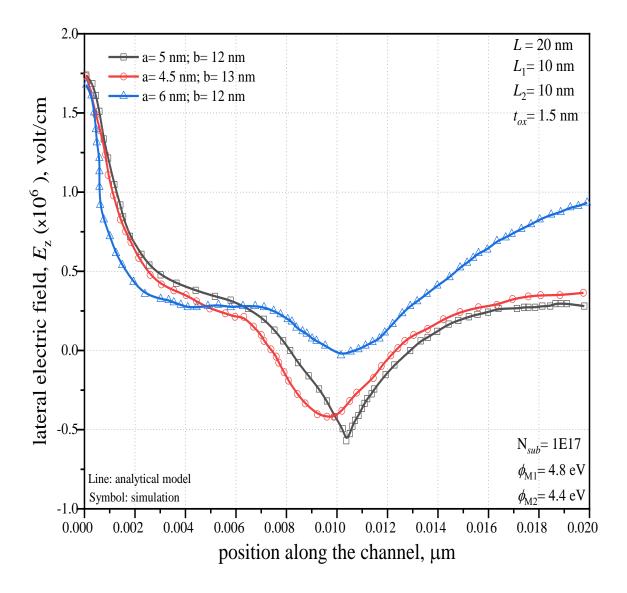

| Fig. 7.9.  | Variation in electric field profile at $L_1$ = $L_2$ for the different internal and external radius of stacked-DMG-CSDG MOSFET.            | 100 |

| Fig. 7.10. | Comparison of lateral electric field distribution in DMG and stacked DMG (at $L_1$ = $L_2$ ) device structure $L$ =20 nm, a=5 nm, b=12 nm. | 101 |

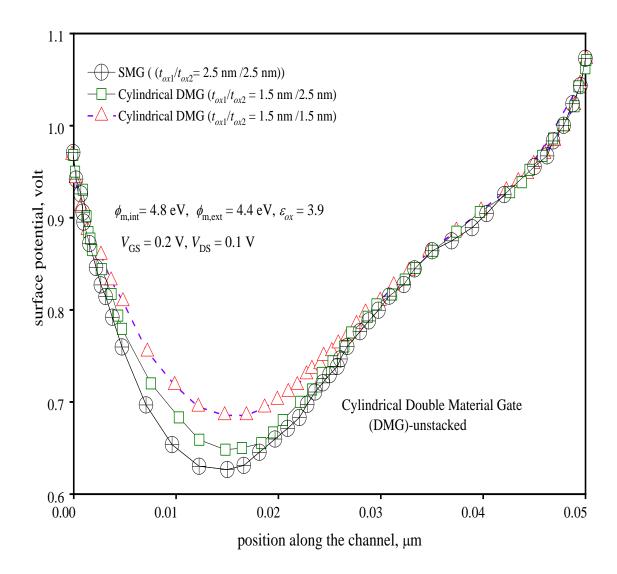

| Fig. 7.11. | Surface-potential profile as a function of the position along the channel for stacked-DMG-CSDG MOSFET at different gate-oxide thickness.   | 102 |

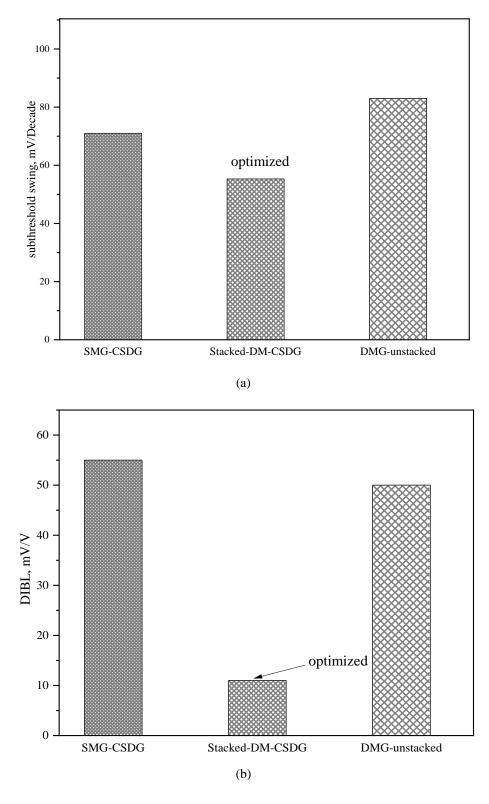

| Fig. 7.12. | Comparison of the different CSDG MOSFET SMG, DMG, and stacked-DMG structures (a) Subthreshold Swing and (b) DIBL.                          | 103 |

## **List of Tables**

| Table No. | Title of Table                                                                                   | Page No. |

|-----------|--------------------------------------------------------------------------------------------------|----------|

| Table 1.1 | Comparison of scaling methods in a MOSFET device.                                                | 20       |

| Table 5.1 | Effect on depletion width due to gate dielectric variation                                       | 66       |

| Table 6.1 | Effect on the variation of doping on maximum depletion width under the gate at strong inversion. | 77       |

| Table 6.2 | Effect of variation of doping on maximum depletion width under the gate at strong inversion.     | 78       |

| Table 7.1 | List of device parameters.                                                                       | 97       |

## **List of Symbols**

| Fermi level potential                       | $\phi_{ m f}$         |

|---------------------------------------------|-----------------------|

| Intrinsic carrier concentration of silicon  | $n_{ m i}$            |

| Bandgap energy                              | $E_g$                 |

| Boltzmann's constant                        | $K_T$                 |

| Built-in potential                          | $V_{bi}$              |

| Carrier drift velocity                      | $v_d^{}$              |

| Channel flat-band voltage                   | $V_{fb,\mathrm{int}}$ |

| Gate-length                                 | L                     |

| Channel thickness                           | $d_c$                 |

| Depletion layer thickness under drain       | $W_{dD}$              |

| Depletion layer thickness under source      | $W_{dS}$              |

| Depletion thickness under the gate terminal | $d_{dG}$              |

| Drain to Source voltage                     | $V_{ m DS}$           |

| Effective channel length                    | $L_{e\!f\!f}$         |

| Electron affinity                           | X                     |

| Electric filed                              | E                     |

| Electron charge                             | Q                     |

| Free space permittivity                     | <b>E</b> 0            |

| Gate-capacitance                            | $C_G$                 |

| Gate-oxide voltage                          | $V_{ox}$              |

| Gate to Source voltage                      | $V_{GS}$              |

| Gate-metal work-function                    | $\phi_m$              |

| Junction depth                              | $X_{j}$               |

| Mobility                                    | M                     |

| Optimum thickness of semiconductor          | $t_{smin}$            |

| Oxide Capacitance                           | $C_{ox}$              |

| Over-drive voltage                          | $V_{ m ov}$           |

| Permittivity of Silicon                     | $\mathcal{E}_{Si}$    |

| Planar depth                                | $W_p$                 |

| Relative permittivity                | $\mathcal{E}_{ ho}$ |

|--------------------------------------|---------------------|

| Semiconductor thickness              | $t_{si}$            |

| Substrate doping concentration       | $N_{sub}$           |

| Surface concentration                | $N_s$               |

| Surface-Potential                    | $\phi_{\sigma}$     |

| Temperature independent pre-exponent | $D_{o}$             |

| Thickness of Gate-oxide Materials    | $t_{ox}$            |

| Threshold voltage shift              | $arDelta V_{ m TH}$ |

| Transconductance                     | $g_m$               |

| Transit time                         | $	au_r$             |

| Transit frequency                    | $f_{ m T}$          |

| Uniform Charge Density               | $ ho_l$             |

#### **List of Abbreviations**

Buried Oxide BOX

Boltzmann Transport Equation BTE

Cylindrical Gate All-Around CGAA

Channel Length Modulation CLM

Complementary Metal Oxide Semiconductor CMOS

Cylindrical Surrounding Double-Gate CSDG

Cylindrical Surrounding Gate CSG

Double-gate DG

Drain Induced Barrier Lowering DIBL

Dual-metal CSDG DM CSDG

Dual-metal Gate DMG

Dual-material Surrounding Gate DMSG

Fin Field Effect Transistor FinFET

Gate-All-Around GAA

Gradual Channel Approximation GCA

Gate Induced Drain Leakage GIDL

Gate Induced Source Leakage GISL

Hot Carrier Injection HCI

Integrated Circuit IC

Metal Oxide Semiconductor Field Effect Transistor MOSFET

Quantum Confinement Effect QCE

Radio Frequency RF

Short-Channel Effect SCE

Single-Metal Gate SMG

Semiconductor on Insulator SEMOI

Surrounding Gate SG

Silicon on Insulator SOI

Technology Computer-Aided Design TCAD

Ultrathin Channel UTC

Very Large Scale Integrated VLSI

#### **Chapter-1**

#### INTRODUCTION

In electronics, the miniaturization of devices and components has been the most significant invention. The semiconductor technology has played a substantial role in the consistent progression of Very Large Scale Integrated (VLSI) devices. Thus far, the current microelectronics engineering has been facing a continuous challenge of increasing system complexity and speed. Over the last 30 years, the most prominent technology element, i.e., transistor, has reduced in size from the micron to submicron and now in a nanometre scales. Such technological advancements have directed the craving for several improvements in the transistor's performance parameters to decrease operating voltage, increase speed, and realize higher packaging densities.

The Complementary Metal-Oxide Semiconductor (CMOS) transistor is a vital device in digital circuits that is the most promising element of an Integrated Circuit (IC) for being a switching component to produce digital logic representation. This chapter provides an introduction starting with the MOSFET as a device with a brief background, challenges associated with the scaling, the evolution of the CSDG MOSFET structure that lays the foundation of the research problem addressed in this thesis.

#### 1.1. MOSFET Overview

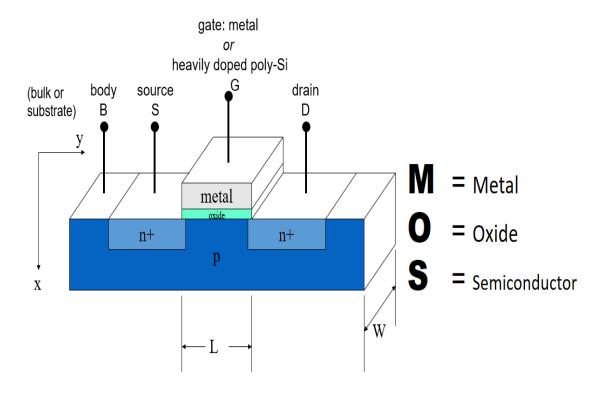

The Metal Oxide Semiconductor Field-Effect Transistor (MOSFET) is the heart of the integrated circuit, is generally used to switch and amplify electronic signals. A MOSFET is an electronic component with a 4-terminal device, namely Source (S), Drain (D), Gate (G), and Body (B) terminals as shown in Fig. 1.1. The body terminal is generally connected internally to the source segment, making it effectually a three-terminal device [1].

In current scenarios, the MOSFET has been the most popular device in the application that has replaced almost all traditional bipolar junction transistors both in analog and digital circuitries. In a MOSFET, the channel's conductivity is developed due to carrier inversion by the augmented oxide field at increasing gate voltages. The forming channel contains electrons or holes, depending on the type of substrate used. They are known as n-type if the substrate is p-type and similarly p-type if it is an n-doped semiconductor.

#### 1.2. Operation Mechanism of a MOSFET

Depending on the mode of operation, the MOSFET is of two types: enhancement and depletion. In an enhancement mode, a potential caused by the field-effect drops across the gate insulator produces the channel conduction through the source and drain contacts. The depletion-mode MOSFETS are in which the channel comprises of carriers at the surface of opposite type to the substrate, and channel conduction destroys with the applied field that diminishes the carriers from the surface layer [2].

Fig. 1.1. Structure of a conventional MOSFET [1].

The depletion-mode MOSFETs are rarely used over the enhancement type because of the uncontrolled conduction irrespective of the applied gate voltage. The metallic gates and the oxide material of a MOSFET have undergone several experiments over the years to improve the device's speed and operation.

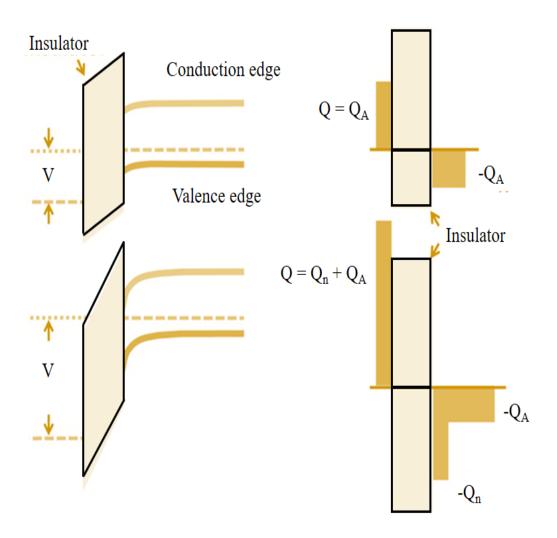

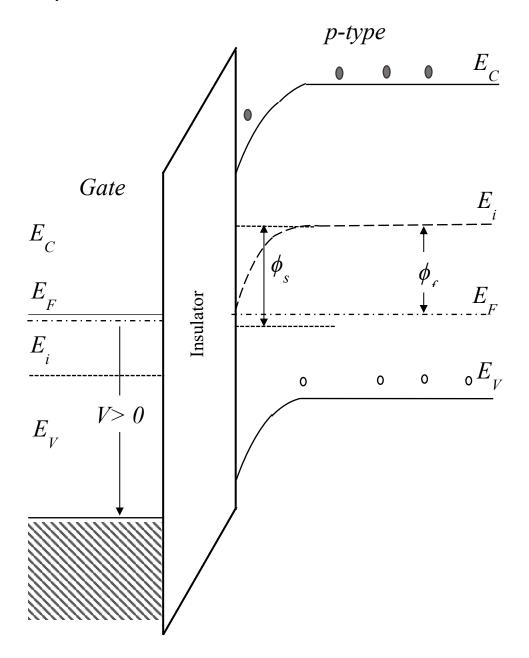

#### 1.2.1. Metal-Oxide-Semiconductor Structure

A Metal Oxide Semiconductor (MOS) structure is formed of a silicon dioxide (SiO<sub>2</sub>) layer grown over a silicon substrate and metal or poly-Si layer deposition. The SiO<sub>2</sub>

dielectric sandwiched between the metal and semiconductor construct a planar capacitor structure. The semiconductor charge sharing gets modified with the application of voltage to a MOS device. In a p-type form, a positive voltage at the gate builds a depletion region produced owing to the movement of holes away from the oxide-semiconductor boundary. Such occurrence results in an area of immovable charges due to negative acceptor ions.

When the gate voltage is increased adequately, the negative charge layer (inverted charge) exists adjacent to the interface oxide-semiconductor interface. In the MOSFET structure, the inversion layer helps in the fast movement of electrons from the source to drain; on the contrary, the MOS capacitor structure has quite a gradual movement due to thermally generated carrier recombination. Typically, the threshold voltage is the term which describes the amount of applied gate voltage to equalize the number of electrons in the inversion layer, same as the holes in the body of the MOSFET device and further increase of the gate voltage after the threshold voltage is identified as gate overdrive voltage.

#### 1.2.2. MOSFET Structure and Channel Formation

The carrier modulation in a MOSFET takes place due to the existence of MOS capacitor structure between the semiconducting substrate and the gate electrode separated by an oxide insulator. The terminal from which the charge carriers (i.e., electrons for an n-channel MOSFET, or holes for a p-channel MOSFET) are originated to stream into the channel is known as the source end, on the contrary the terminal through which charge carriers are leaving out via the channel is known as the drain end.

The occupied energy bands in the semiconducting materials are well defined by their relative situation of the Fermi level. Fig. 1.2 shows channel formation in an n-channel MOSFET. The applied gate bias above the threshold voltage drift the holes present in the substrate away from the gate and results in the shifting of the valence band away from the predominant Fermi energy level [3].

If the gate bias continues to increase further, it results in carrying the conduction band nearer to the Fermi level, which inhabits the surface with more of the charges inversion layer and forms the channel of n-type. The conducting channel expands between the source and the drain through which progressive current conduction takes place. With the increase

of the gate voltage, the electron density populates in the inversion layer, which further results in the flowing current between the source and the drain. The channel is lightly populated if the gate voltage is below the threshold voltage and only a negligibly small subthreshold leakage current is attained.

The channel becomes p-type if the negative gate to source voltage is applied and operates similar to the n-type device except for opposite polarities of charges and voltages. At low negative gate bias with magnitude below the threshold value vanishes the p-channel, and a small leakage current can flow.

Fig. 1.2. Channel formation in n-channel MOSFET [3].

The MOSFET device can be made in a manner in which the semiconductor layer is over a buried-oxide (BOX) known as Silicon on Insulator (SOI) design. When the channel positioned in the middle of the BOX and gate insulator is precisely thin, then such arrangement of the device is known as an ultrathin channel (UTC). Alternatively, in another configuration, the device is made above a non-silicon semiconducting material layer is a semiconductor on insulator (SEMOI) device.

#### 1.3. Scaling of Transistor

At reducing transistor size for attaining higher complexity of integration, the fabrication of the device becomes cumbersome. For example, the ICs turn out to be denser when the devices undergo downscaling, the lithographic process, interconnections, or processing steps of device manufacturing becomes challenging. Therefore, increased device performance, such as improved switching speed and reduced power consumption, are desirable while scaling down the device to a smaller size.

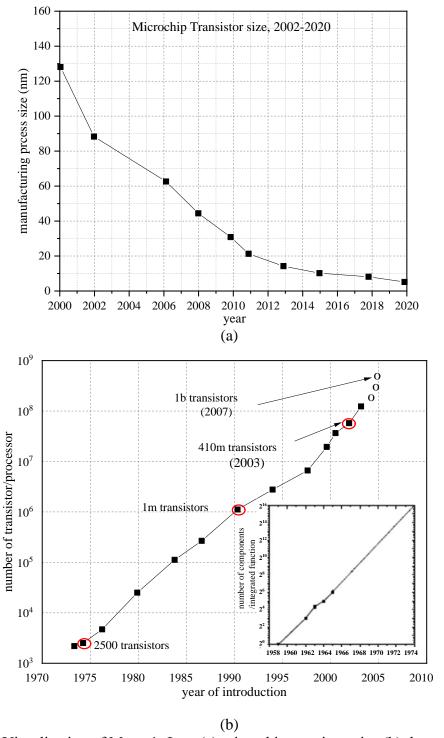

The device downscaling has captured significant attention in microelectronics device research, and the current progress of CMOS-based electronics has witnessed this in the last few decades. The density of transistors in a chip has been firstly predicted by the cofounder of Intel Inc. Gordon Moore, which is well-known as Moore's law [4]. His law has driven the industrial projection starting from 1975 for more than forty years with the assumption of number of transistors per chip getting double every year. It has been a successful era in the semiconductor industrial growth that the prediction reported well in advance about the possible integration of  $6.5 \times 10^4$  components into a single chip achieved in 2007. Fig. 1.3 (a) illustrates the follow-up of the predicted progress trend of the semiconductor industry. About 32 actual transistors in the first anticipation of this law have reached nearly 0.5 billion transistors integrated in the present, as shown in Fig. 1.3 (b). Such an enormous growth of component integration has proven that the idealistic prediction was incredible, following which it has been vital to facilitate the reduction of the discrete transistors.

The MOSFET scaling has been the essential constituent in the digital, semiconductor technological revolution, leading us to the present age with immensely multifaceted

devices and systems [5]. It is noteworthy that "Moore's law" has been inferred in another way at the different progressive phases of the technology growth. A consensus accepted that "the number of components per chip doubles every 1.5 years".

Fig. 1.3. Visualization of Moore's Law (a) microchip transistor size (b) the transistors' numbers commercially integrated into the processor. Source: Intel Inc. [4].

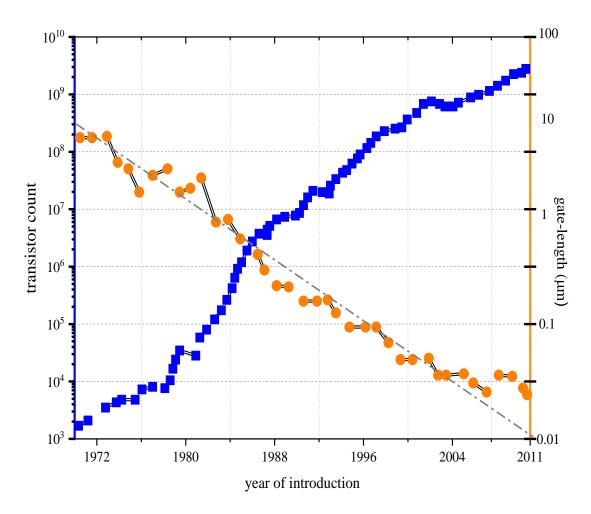

However, as in the inset shown in Fig.1.4, the original speculation of Moore was components per chip doubling up every year. Indeed, in the beginning, the stated rate of development was well retained up till the 1970s and continued to the early 1980s. Later, in the last three decades, the device dimensions have experienced been an extensive reduction.

Fig. 1.4. Number of transistors and gate-length reduction over the years [5].

The trend of reducing the number of transistors and gate-length over the years is shown in Fig. 1.5. It can be perceived that since its initiation, the device design in the 1970s that having the least feature-length of 10 µm had a steady reduction down the line up till 2000 to 0.15 µm of the size. It was an approximate reduction at a 13% rate during those years [6]. However, the appropriate scaling does not only mean a decrease in the gate-length and width, but all the other dimensions such as gate/source and gate/drain alignment, oxide thickness, and depletion-widths are also involved.

Fig. 1.5. Performance of high-speed Microprocessor unit and the functionality versus the year of technology nodes: source ITRS 2004 update [6].

#### 1.3.1. Benefits of Scaling

The data rate capacity depends on the number of logical transistors in a memory chip, termed as functionality in the microprocessor units [7]. Integrating components in a single chip has been growing day by day. Such increasing compactness is in the form of increasing functionality per chip and increasing density, as shown in Fig. 1.5. Therefore, the primary benefit of scaling can be given as follows:

- 1) To achieve high device packing density,

- 2) To improve frequency response, and

- 3) To improve the current drive (transconductance g<sub>m</sub>).

#### 1.3.2. Types of Scaling

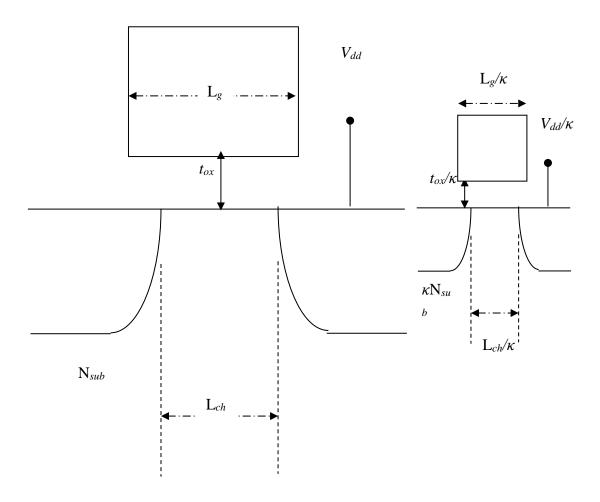

There are two types of commonly known scaling methods: constant-field scaling and constant-voltage scaling [8]. The constant electric field scaling is based on reducing the operating voltage such that the magnitude of the electric field (vertical or horizontal) stays constant while the transistor dimensions, including the gate-length, the gate oxide thickness, and the supply voltage, are scaled by the identical factor  $\kappa < 1$ .

Fig. 1.6. Sketch of MOSFET Scaling [8].

The scaling approach of the constant electric field scaling situation proposed by *Dennard* et al. [9] is shown in Fig. 1.6. However, it produces an enormous decline in the power-delay product of a different transistor. On the contrary, a constant-voltage scaling is conceived on voltage compatibility with previous circuit topologies keeping the supply and the terminal voltages are kept unaltered.

Table 1.1. Comparison of scaling methods in a MOSFET device.

| Parameter (Symbol)                    | Constant-<br>field Scaling | Constant-voltage<br>Scaling | Constant-<br>voltage scaling<br>with velocity<br>saturation |

|---------------------------------------|----------------------------|-----------------------------|-------------------------------------------------------------|

| Gate-Length (L)                       | $1/\kappa$                 | $1/\kappa$                  | $1/\kappa$                                                  |

| Gate-Width (W)                        | $\kappa^2$                 | $\kappa^2$                  | $\kappa^2$                                                  |

| Gate insulator thickness ( $t_{ox}$ ) | $1/\kappa$                 | 1/ <b>K</b>                 | $1/\kappa$                                                  |

| Electric filed (E)                    | 1                          | κ                           | κ                                                           |

| Substrate doping (N <sub>sub</sub> )  | $\kappa^2$                 | $\kappa^2$                  | $\kappa^2$                                                  |

| Gate-capacitance ( $C_{\rm G}$ )      | $1/\kappa$                 | $1/\kappa$                  | $1/\kappa$                                                  |

| Insulator capacitance ( $C_{ox}$ )    | κ                          | κ                           | κ                                                           |

| Transit time ( $\tau_r$ )             | $1/\kappa^2$               | $1/\kappa^2$                | $1/\kappa$                                                  |

| Transit frequency $(f_T)$             | κ                          | $\kappa^2$                  | κ                                                           |

| Voltage (V)                           | $1/\kappa$                 | 1                           | 1                                                           |

| Current (I)                           | $1/\kappa$                 | κ                           | 1                                                           |

| Power (P)                             | $1/\kappa^2$               | κ                           | 1                                                           |

| Power delay $(P\Delta t)$             | $1/\kappa^3$               | 1/K                         | 1/ <b>K</b>                                                 |

The comparative list of design factors and parameters of different scaling methods is shown in Table 1.1. It has a drawback that the electric field rises when the minimum feature-length is compacted. Several second-order effects such as velocity saturation, mobility degradation, increased leakage currents, and lower breakdown voltages exist at reduced device's dimension.

The comparison is shown among the constant-field scaling, constant-voltage scaling, and the constant voltage scaling in the presence of velocity saturation [8].

#### 1.3.3. Scaling Challenges

The challenges in scaling the device include the need for strategies to reduce subthreshold conduction, leakage minimization in gate-oxide and junctions, reduced output conductance and transconductance, and diminishing interconnect capacitance, normalizing heat production, and other process and modeling complexities [2-4]. The issues that arise in scaling the device involve overcoming the trade-off among the power consumption, short-channel effects (SCEs), and the low current. As the traditional MOSFETs fail to attain the desired device performance, alternative device structures for further scaling had been continuously explored.

#### **1.4.** Short-Channel Effects (SCEs)

The gate-length is one of the most significant constraints associated with transistor scaling. Smaller gate-length allows the more significant drive current and subsequently fast-speed operation as the parasitic capacitances are also scaled. Therefore, high performance at the lower voltages is operational [13].

The actual channel length is determined by deducting the over-all lateral diffusions of the source and the drain from the device's physical gate length. The physical gate length is more than the actual length; however, the difference  $(Lg - L_{ch})$  cannot be computed exactly. When the actual length is scaled down, at specific consented points, so-called SCEs appear, which is not experiential otherwise.

The SCEs are abandoned if the device is a long-channel; nevertheless, the device performances are badly affected [14]. The MOSFETs at short-channel encounter the following significant phenomenon. In short-channel devices:

- 1) Two-dimensional electric field profile that results in the reduction in the threshold voltage and Drain-Induced-Barrier-Lowering (DIBL),

- 2) Very high electric field strength in the channel introduces impact ionization Hot Carrier Injection (HCI), and the breakdown and parasitic effect,

- 3) Limitation imposed on electron drift characteristics brings mobility degradation and carrier velocity saturation,

4) Physical separation between the source and the drain decreases, familiarizing channel length modulation, and Punch-through phenomena.

#### **1.4.1.** Two-Dimensional Field Profile (*V*<sub>TH</sub> Reduction and DIBL)

The potential field distribution turns into a 2-dimensional form instead of a unidimensional profile due to channel length reduction with scaling. Consequently, the channel's charge-control, i.e., charge sharing among the gate, substrate, source, and drain, originates. Further, the region's depletion depth is supplemented by a high surfacepotential that attracts more conducting charge and current from the channel, influencing the threshold voltage reduction.

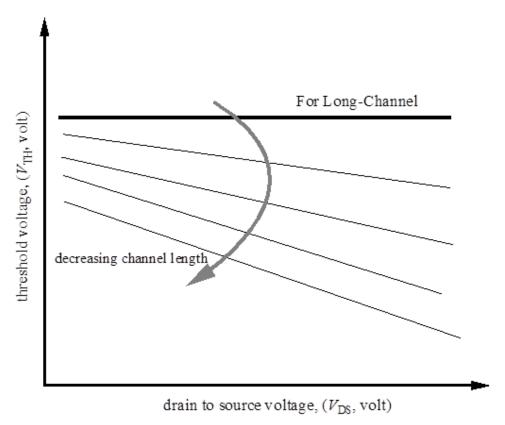

The effect on threshold voltage due to reducing channel size is depicted in Fig. 1.7. The arc that represents decreasing threshold voltage with the declining effective length is known as  $V_{\rm TH}$  roll-off, which is probably an intimidating barrier in future MOSFET design. The minimum acceptable length for the channel is mainly decided using the roll-off characteristics.

Fig. 1.7. Effect of channel length reduction on threshold voltage [15].

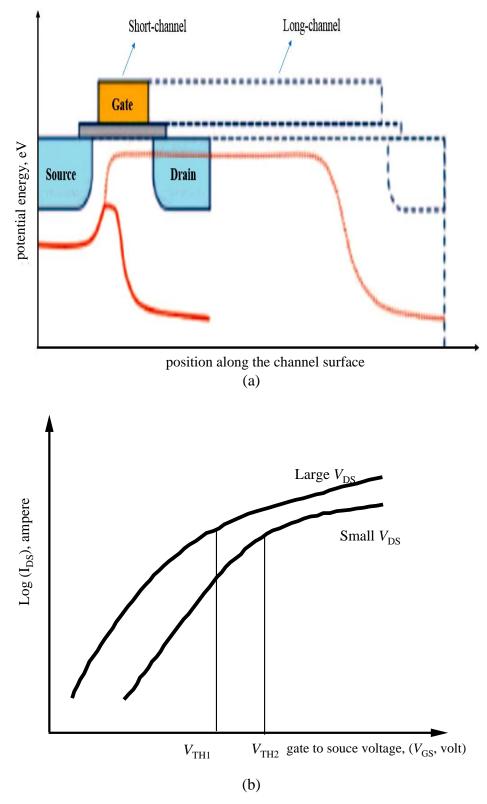

Fig. 1.8. DIBL (a) illustration of the effect, (b) effect on the current characteristics.

As illustrated in Fig. 1.8 (a), a variation of the threshold voltage at a shorter gate-length device is controlled by the applied drain voltage to affect the inversion charge initially caused by the high drain voltage [16].

Accordingly, the gate voltage or turn tin voltage  $V_{\rm TH}$  is influenced due to the field distribution close to the drain. Such occurrence can be omitted using an appropriate scaling of the drain and source depths, maintaining the substrate doping concentration. The Drain-Induced-Barrier-Lowering (DIBL) effect exists if the gate-length reduction occurs in the absence of accurate scaling of the other device dimensions, then the drain affects the output conductance and threshold voltage as shown in Fig. 1.8 (b).

#### 1.4.2. Very High Electric Field Strength (Impact Ionization)

The longitudinal field in the device channel is inclining and increases from the source to the drain region. In the scaled device, source and drain adjacent junctions lead to the highest field at the drain that deteriorates alongside the channel. The charge carriers gain extra-energy due to increased field and get accelerated with an increased velocity. A charge that passes through the inversion channel at the pinch-off condition in the direction of the drain accelerates faster to attain maximum kinetic energy when in saturation. High energy charge-carriers are referred to as hot-carriers and can create silicon lattice-collision with their acquired power that impacts impact ionization [17].

#### 1.4.3. Mobility Degradation and Carrier Velocity Saturation

In particular, the inversion layer's mobility in the device is lesser than that of the substrate due to electron wave function expansion over the low mobility gate insulator. Typically, the surface electric field is higher in the short-channel devices, bringing an extra-impulsion to the electron wave-function into the gate insulator known as field-dependent mobility. Therefore, the mobility at the surface weakens with the electric field, known as mobility degradation. It happens in two ways: mobility reduces with the increasing gate voltage due to the vertical electric field and the other when the mobility decreases with the drain potential by the parallel electric field [18].

Fig. 1.9. Velocity saturation in short-channel device (a) nonlinear operation, (b) critical electric field [18].

In general, the electric field's combined effect altogether drives the electron transport, the lattice-scattering, the impurity, and the other charge control in the device. When the electric field (E) is low, the mean velocity of charges ( $v_{drift}$ ) is proportional to the electric field, i.e.,  $v_{drift} = \mu E$  with proportionality constant as charge mobility ( $\mu$ ). The drift velocity at saturation ( $v_{SAT}$ ) for the critical electric filed ( $E_C$ ) is given by:

$$v_{\text{drift}} = v_{\text{SAT}} = \mu E_{\text{C}} \tag{1.1}$$

However, the relationship does not follow linearity at the higher electric field due to scattering delays across the channel length (L), therefore drain saturation voltage ( $V_{DSAT}$ ) can be written as:

$$V_{\rm DSAT} = E_{\rm C}.L = \frac{v_{\rm SAT}.L}{u} \tag{1.2}$$

and,

$$I_{DSAT} = v_{SAT} C_{ox} W \left[ (V_{GS} - V_{TH} - \frac{V_{DSAT}}{2}) \right]$$

(1.3)

where  $I_{DSAT}$ ,  $C_{ox}$ , and W are the drain saturation current, oxide capacitance, and the channel width of the MOSFET, respectively. When electric field energy is more than the carrier energy, the velocity gets saturated to  $v_{SAT}$ . The situation concerns the drain current shifting to the nonlinear operation, as shown in Fig. 1.9 (a).  $E_c$ , known as the critical field, introduces velocity saturation in the short-channel device as depicted in Fig. 1.9 (b).

The critical field is of order  $\sim 10^6$  V/m. Due to velocity saturation, results in saturation current ( $I_{\rm DSAT}$ ) to endure smaller values than to the idealistic correlation, yielding further for a reduced saturation current ( $V_{\rm DSAT}$ ) [19]. The velocity saturation occurs before reaching the pinch-off condition, and accordingly, the saturation appears even at the low drain voltage values. Therefore, the short-channel devices are more frequently inclined to switch operation in extended saturation conditions.

#### 1.4.4. Channel Length Modulation (CLM) and Punch-Through

The channel's actual length tends to reduce with increasing drain potential as the drain depletion region widens, known as the channel length modulation (CLM). Referring to Fig. 1.10 (a), in the long channel devices, actual length decrement is insignificant compared to the total channel length, while it is highly affected in a short-channel device

that reduces the channel length towards zero. Also, both the depletion width regions can touch, resulting in a massive drain current as depicted in Fig. 1.10 (b).

Fig. 1.10. (a) Representation of Channel length Modution and (b) punch-through condition in short-channel MOSFET[21].

position along the channel

(b)

$\boldsymbol{x}$

The drain comes very close to the source due to the drain depletion region's extension and forms a distinct depletion region [21]. Consequently, the source-drain potential makes a stronger field under the gate region, which opens the obstruction of current undesirably to switch the transistor to an abrupt turn-on. This is essentially equivalent to reducing the transistor's threshold voltage, which leads to a higher leakage current.

The resultant actual length is equivalent to the metallurgical size minus the depletion widths of the source/drain part. An extreme case of the CLM is known as punch-through.

#### 1.5. Background and Evolution of CSDG MOSFET

As the most critical device component of modern electronics, the MOSFET has a persistent history of rigorous reforms and phenomenal scaling traced from Moore's prediction of shrinking device size and package density.

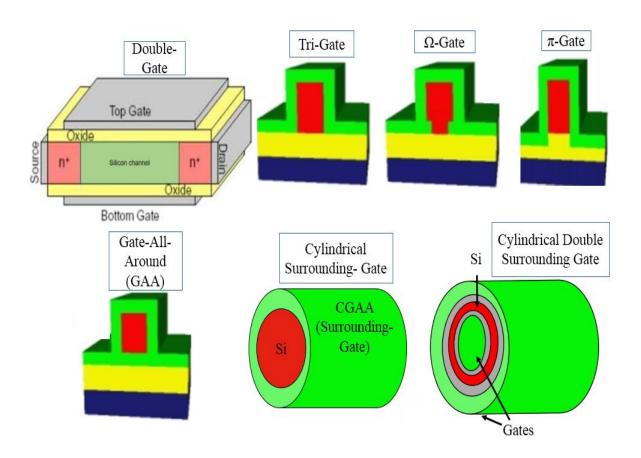

Fig. 1. 11 Multigate and surrounding gate MOSFET structures [26].

The scaling of dimensions which exceeds two orders of magnitude in the past decades has undergone extensive physical modifications besides addressing the gate-control for optimum performance of the device [22]. The rapid decrease in the device dimensions with Moore's law's advent follows several problems such as Short-channel Effects (SCE's) and Hot Carrier Effects. In the last three decades, there have been extreme efforts to minimize the SCEs and the improved gate controllability utilizing various structural modifications [23, 24]. These problems have been mitigated by the introduction of multiple gates in the structure and invention of different geometries for MOSFETs. Fig. 1.11 shows the sketches of various multigate structures such as Double-Gate (DG), Triple Gate, Omega-Gate, FinFETs, Surrounding Gate (SG), Cylindrical Surrounding Gate (CSG), and so forth [25-27]. The Surrounding Gate (SG) structures have attained much popularity among the multiple-gate forms as the gate has been exhaustively enclosed by the entire semiconductor channel, which significantly enhances the gate control over the channel. As proposed by Srivastava et al. [28], the Cylindrical Surrounding double-gate MOSFET has been one of such prominent gate-all-around devices.

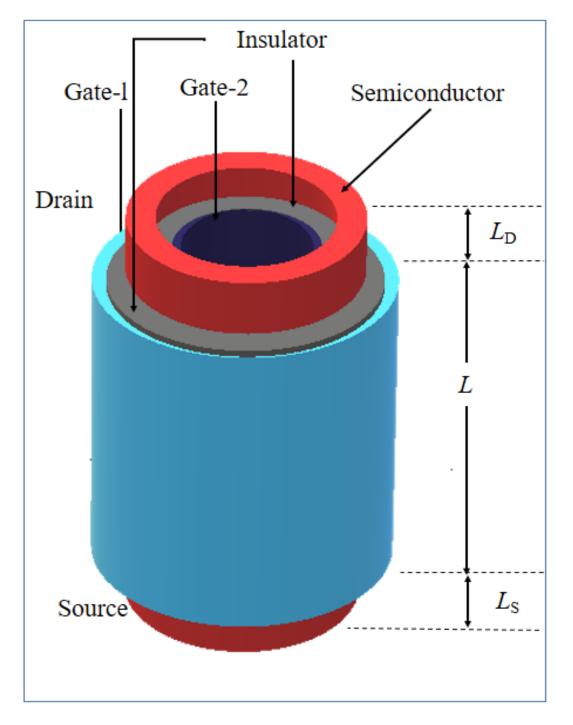

Fig. 1. 12 (a) Schematic of Cylindrical Surrounding Double-Gate (CSDG) MOSFET structure.

The device with superior control over the channel with a large driving current has been highly anticipated. The structure, proposed initially has been featured as two concentric cylindrical gates accommodated in a single transistor, enabling the device with improved control over the channel.

In particular, the structure can be perceived as a double-gate MOSFET wrapped up from the end to end founding in a cylinder as shown in Fig. 1.12. The device's inherent characteristics, including the small-signal analysis, electrical parameters, and several other applications, have been conveyed in recent years [29]. Past research confirms the potential of the CSDG for inventive circuits, wherein independent adjacent gates of CSDG enhances circuit design flexibility. The electrical and physical parameters analyzed at the device's operating conditions can control the device behavior in circuit design, resulting in improved performance. The effect of doping, analytical modeling, and enhanced characteristics have been obtained using CSDG MOSFET [30].

The analysis for obtaining improvements in the device parameters based on explicit, low frequency, equivalent capacitance model in CSDG MOSFET has potentially been reported as a significant contribution to microelectronic device research [31, 32]. A device must have higher carrier transport and drive current; therefore, either a more inventive design or the modified device physics of the existing CSDG structure seems necessary. The device modification can primarily realize enhanced electrical performance in terms of the low electric field towards the drain side, surface-potential, drain current,  $I_{\rm on}/I_{\rm off}$ , transconductance, and input gate-capacitance.

### 1.6. Device Compact and Analytical Modeling

A physics-based device model is defined as a depiction of device actions described in analytical, numerical, or mathematical terms. On the contrary, the device simulations approximate numerical expressions to explain some complex equations, such as partial differential equations. Moreover, device models may be characterized as compact if described in terms of analytical and explicit terms. The compact models can also cover reproductions that involve pre-processing of model expressions using iterative procedures to result in lookup variables for a fast recovery for a solution in the simplified models. The

compact models have the feature of intelligent computation in the event of circuit models and simulation.

#### 1.7. Objective of the Research Work

The research objective is to analyze the gate material engineering in the Cylindrical Surrounding Double-Gate MOSFET structure with a device physics-based modeling. Moreover, mathematical derivation and analysis of the electric field and pinch-off capacitances are to be established. Further, numerical solution and silicon thickness inducing CSDG MOSFET parameters can lead to the understanding of thickness optimization. To derive and analyze the optimum semiconductor thickness depletion depth under the source-drain region, the channel's depth in the semiconductor of a CSDG MOSFET at strong inversion for recognizing the dependence parameters at drain-source bias. Finally, the model analysis of a dual-material gate in CSDG MOSFET is obtained by comparing surface-potential and electric field profiles in gate-metal research designs.

#### 1.8. Research Questions

This section contains and describes the questions with their answers posed and investigated during this research work.

# Q1: What will be the shape of the gate-oxide capacitor of the CSDG MOSFET structure at the device pinch-off operation?

Answer: In the cylindrical Metal-Oxide-Semiconductor structure of CSDG, at the device pinch-off, the semiconductor electrode becomes a cone shape region of conducting effectively. Therefore, unlike other cylindrical capacitor shapes, it assumes a truncated cone. The research problem has been addressed, and the actually anticipated sketch of the structure is demonstrated in Chapter-3.

### Q2: How does the gate oxide-capacitance depends on the device dimension in CSDG MOSFET?

Answer: The expression reveals that the capacitance at pinch-off is not a direct rationale of cylindrical sizes of the device; instead, it takes a complex algebraic and logarithmic fractional form as resulted in the expression, which is comprised of the external, internal

dimensions, thickness, and material properties of the capacitive layer in the CSDG structure.

### Q3: Is the gate-oxide capacitance of CSDG MOSFET is identical in all region of operation?

Answer: No, the oxide capacitance is affected by the physical capacitor plate's shape change at a pinch-off operation due to charge sharing.

# Q4: How to calculate electric field due to oxide capacitance in a typical CSDG MOSFET geometry having distinct gate-assembly?

Answer: The electric field analysis due to oxide capacitance in CSDG MOSFET evolves with its structure that has a combination of two cylindrical capacitors. Therefore, first deducing the electric field's expression of each capacitor individually and further taking the algebraic sum of the specific solution is a convenient method to calculate, which results in the total electric field due to oxide capacitances.

## Q5: What are the approximate device physics parameters on which the silicon (or semiconductor) thickness of CSDG MOSFET depending upon?

Answer: The CSDG MOSFET structure needs to incorporate analysis based on existing firm device physics or models to understand the variability.

### Q6: How the gate-metal work function affects the electrical characteristics in CSDG MOSFET?

Answer: As the work-function is a prominent electronic property of metal, the gate metal can directly move the changes in ionic behavior of the channel, affecting the flat-band voltage and hence the device's threshold characteristics. By an appropriate pursuit to the gate-metal work-function, the internal gate's threshold voltage could be transformed to a lower than the external gate with correspondingly lower the work-function of internal gatemetal.

### Q7: What will be the effect of two different gate work functions on characteristics in CSDG MOSFET?

Answer: The physics and behavior change in the source and the device's drain side takes place with different gate metals. The gate metal engineering tends to increase the undesired off-current; however, it also increases the current in a similar proportion. Furthermore, the metal with low work-function on the drain side drops the drain bias across the region. It

tends to decay in the direction of the drain end, which leads to a decline of Drain-Induced-Barrier-Lowering (DIBL) and channel length modulation effects. Further, the internal gate's threshold voltage ( $V_{\rm TH1}$ ) could be reduced compared to the external gate ( $V_{\rm TH2}$ ) by arranging the gate metal work-function in Double-Gate devices.

# Q8: What gate metal architecture in CSDG MOSFET can be thought of for SCEs improvement?

Answer: As the device design and analysis in a gate-stacked and dual-metal gate structure can be found in the previous literature; therefore, it would be insightful to primarily implicate an unstacked and stacked gate metal design in CSDG MOSFET.

## Q9: How is the surface-potential distribution affected by changing the length of specific metal in a dual-metal stacked structure of CSDG MOSFET?

Answer: In the dual-metal stacked structure, the surface-potential step-change is anticipated, which leads to a growth in the carrier velocity and a further increase in carrier transport efficiency of the device. The effect, in turn, increases the drain current of the device. Furthermore, it can be practical that the minima of surface-potential shifts towards the source side, which lies underneath the region of higher work-function metal.

# Q10: How is the electric field distribution affected by changing the length of a specific gate metal portion in the dual-metal stacked structure of CSDG MOSFET?

Answer: In a MOSFET device, changing the length of specific metal causes relocation of the lateral electric field closer to the source region, and the uniformity of the electric field in the channel enhances. Moreover, the electric field minima distributed along the channel positions of metal interfaces are changed with the specific metal region's length. If the CSDG MOSFET analysis is done with a dual-metal gate design, the advantages of gate-metal engineering can be replicated.

#### Q11: Which methods can be relevant to approximate the channel thickness?

The depletion depth theory to develop thickness analysis for the CSDG MOSFET structure would be appropriate based on the well-known Dang's model approach of charge sharing.

## Q12: How can the thickness dependence be compared in the CSDG MOSFET structure with the planar MOSFETs?

Answer: The CSDG structure is a unique structure derived from the cylindrical orientation of double-gate MOSFET. The device design has several benefits as it provides better gate

control due to surrounding gate geometry. A planar structure and CSDG MOSFET depletion-width computation, including doping and bias voltages, should be made side-by-side to accomplish the firm estimation.

#### 1.9. Research Contribution of this Thesis

This thesis aims to analyze and incorporate the impact of gate material engineering in the CSDG structure with a device physics-based modeling to combat the effect of SCEs. To attain the objective, in particular to the proposed design, an electric field, capacitance, and other characteristics parameters have been calculated at a pinch-off to analyze the capability of CSDG MOSFET. Further, this thesis work provides insights into the thickness of the device parameter dependence that has been mathematically analyzed in detail at the onset of strong inversion. Finally, a design and numerical analysis of dual-material gate and gate-stack in the CSDG MOSFET have been explored.

#### 1.10. Organization of the Thesis

The research work presented in this thesis has been organized in chapters as follows:

Chapter 1 provides an introduction starting with an overview of MOSFET and a brief background, challenges associated with the scaling, understanding the short channel effects, development of the CSDG MOSFET structure, research questions, and objective places the foundation of the research addressed in this thesis.

Chapter 2 details the literature review, including the trace of the research progress made in analytical model developments, gate-capacitance modeling, progress in CSDG MOSFET research, gate material engineering, and motivation thesis research work.

Chapter 3 describes the analytical research of gate-oxide capacitance in CSDG MOSFET, particularly at the device pinch-off condition by deducing the oxide capacitance for the internal gate and external gate assembly the device and summarized the obtained results.

Chapter 4 deals with the electrical field analysis due to gate-oxide capacitances explaining the model derivation for CSDG MOSFET and the summary results.

Chapter 5 specifies the research work of the depletion width analysis in MOSFET device with details of depletion depth in MOSFET.

Chapter 6 includes the analysis of thickness in CSDG MOSFET founded upon the depletion depth model concept at the onset of strong-inversion, including the evolution of depletion depth, optimum semiconductor thickness, and result from analysis with a chapter summary.

Chapter 7 comprises the details of the novel Dual-Metal Gate architecture included in the CSDG MOSFET. The detailed description of the stacked designs concept, model formulation, derivation of the surface-potential, the gate charge, and the threshold voltage has been elaborated with the comparative results.

Finally, Chapter 8 concludes the research work presented in this thesis and recommends the future work scope.

### **Chapter-2**

### **REVIEW OF LITERATURES**

This chapter provides detailed research progress in developing analytical, explicit, or compact models for various MOSFET structures. This chapter's subsections describe the comprehended literature study organized to portray the background of chronological progress in reaching the analytical models of different device structures, understanding progress made in CSDG MOSFET, and other relevant efforts made that laid the foundation of the research problem and motivation of this research work.

#### 2.1. Review of Analytical Models Developments

Oh et al. (2000), in their work, have compared the electrostatic potential confined by the gates of DG and CSG MOSFET using the Evanescent-Mode Analysis (EMA) solution. They have notified that the device dimension of cylindrical surrounding-gate (CSG) MOSFETs is much reduced (to 35 percent shorter of the actual lengths than double-gate MOSFETs) Silicon, the insulator thicknesses in the CSG MOSFETs can be better scaled up for mitigation of SCE [33].

Jimenez et al. (2004) have presented a validated a simplified, compact model for lightly doped CSG MOSFETs based on the meticulous solution of the Poisson's and the continuity equation deprived of the charge-sheet approximation to describe the inversion charge distribution in the channel.

Further, it was confirmed that a simple analytical *V-I* model is suitable for compact modeling of undoped (lightly doped) SGT MOSFETs. The model was reportedly capable of an accurate description of all regions of operation. Specifically, the inability to capture volume inversion using the charge-sheet approximation had been well addressed in their work [34].

Aouaj et al. (2005) have deduced the 2-D analytical model using EMA for an fully depleted. cylindrical/surrounding gate device structure to compare Surface-Potential and threshold voltage with the other models. Their work revealed characteristic length dependence, which is governed by silicon and oxide thickness [35].

Quenette et al. (2009) have proposed an innovative, dynamic charge sharing model for 45 to 65 nm technology nodes for electrical characterization and compared it with the charge sharing  $V_{TH}$  model to enhance the device performance at low power consumption memory application. They reported the electrostatic characteristics of experimental data in terms of SCEs DIBL, subthreshold slope variations, and  $V_{TH}$  dependence and suggested improved capacitive response of the device in non-volatile memory applications [36].

Verma et al. (2015) have proposed a physics-based model for their surrounding double-gate nanowire MOSFET structure based on the solution of 2-D Poisson's equation and superposition of the coordinate system. Using the simultaneous validated simulation, they reported the influence of channel length variation on the double surrounding gate device's electrical behavior and indicated double-gate CSG's superior performance over the single CSG MOSFET [37].

Jena et al. (2015), in their research of scaling comparison of the device design, have explored and described an undoped Cylindrical Gate All Around (CGAA) structure. Further, based on their device results [38], they suggested the utility of the device structure's undoped nature for suppressing SCEs and other scaling complications.

Verma et al. (2016), in the research work [39], have presented the modeling and simulation of CSDG MOSFET with an alternative gate insulator as vacuum than SiO<sub>2</sub> for improvement of hot-carrier reliability and radiofrequency RF performance. They concluded that the vacuum as a gate dielectric could substitute the double surrounding gate in a CSG form for evading the inconsistencies raised by the hot-carrier injection.

Sood et al. (2016) have analyzed the performance of various parameters for the surrounding-gate MOSFET device and informed the influence of Gaussian doping on the undoped device's electric potential and electron density [40]. They reported that the surrounding-gate devices have been better in terms of unilateral and maximum power gain in the RF applications.

Basu et al. (2017) have proposed an analytical model for the electrical characteristics of surrounding gate MOSFET in strong inversion by solving simplified 1-D Poisson's equation in conjunction with the rectangular and cylindrical coordinates for device boundary condition. The designed device was reported with a high concentration of

inversion charges that significantly influenced their research to obtain more excellent gate controllability [41].

Nandi et al. (2017), in a paper, have developed an analytical model of double-gate MOSFET using Green's function approach in the subthreshold regime of operation [42]. The method was reported useful for forecasting the electrostatics of devices in which the S/D lateral electric field is of prime significance.

Taur et al. (2018) have demarcated a double-gate MOSFET model that pushes substantial revisions in the gradual-channel estimation approach using lateral field gradient.

It has been specified in their model that when saturation occurs and goes beyond, the channel pinch-off does not happen, which leads to only limited output conductance [43]. The method proposed by them can improve the output conductance in the saturation region of operation.

Agarwal et al. (2018) have described a two-dimensional surface-potential model in gallium-arsenide-based nanowire GAA MOSFET using appropriate boundary conditions and informed the performance parameters. Their efforts have been promising for the utilization in compact modeling [44].

Uchechukwu et al. (2019) have analyzed the threshold voltage and subthreshold swing of a CSDG MOSFET using EMA and compared the other models such as polynomial exponential and parabolic potential approximation (PPA) [45]. As a significant gain, the threshold voltage roll-off has been optimized in their research by reducing the oxide thickness and diameter of the Silicon of the device structure.

Sharma et al. (2004) have explained the current conduction progression using fabrication of nanowire wrap-around-gate Silicon MOSFET to investigate and compare SOI top-only-gate planar MOSFET. It was suggested that a significant increase in current density is possible in the nanowire devices compared to the planar devices [46].

In their work, a semi-empirical carrier mobility relation for the non-planar device was used by them. The experimental results showed that the current was a linear function of the number of wires.

#### 2.2. Review of Progress in Gate-Capacitance Analysis

Moldovan et al. (2006) have developed gate-capacitance analytical expressions for undoped surrounding gate MOSFETs using a unified charge control approach to derivate the small-signal model. They have verified the model parameters' boundless continuity in desirable proximity with the 3-D numerical simulations of modeled capacitances. They have described the correlation mobile charge sheet density among current, total charges, and capacitances for the channel boundaries [47].

Ruiz et al. (2010) proposed and comprehended a comparison of the model for total gate-capacitance of the CSG transistor and DG, accounting for both dielectric capacitance and the inversion capacitance [48]. Their study explained the mobility degradation due to capacitive charges in the two devices, increasing short-channel device consideration. Moreover, they have highlighted the impact of gate insulator's low thickness in modifying the inversion and gate-capacitance.

Cousin et al. (2011) have enlightened research on a unified compact model of undoped short-channel GAA MOSFETs and established a continuous explicit method that endorsed all regions' operation [49]. Their proposed approach was convenient, as reported in the validated model simulations.

Marin et al. (2013) have demonstrated effective gate-capacitance modeling of nanowire structure devices, including the quantum confinement of oxide-capacitance, density of energy states, and the charge scattering in the nanowire [50]. They showed a comparison of device capacitive behavior with III-V group material nanowires and the Silicon-based alternatives. Their work suggests an accurate description of gate-capacitance and defines the current drain model at device pinch-off.

#### 2.3. Research Progress in CSDG MOSFET