# University of Natal

# FEASIBILITY STUDY OF A NEURAL NETWORK CURRENT CONTROLLER FOR A BOOST RECTIFIER

by

# Cedric Alwyn Worthmann

Submitted in fulfilment of the academic requirements for the degree of Masters of Science in Engineering in the Department of Electrical Engineering of the University of Natal in South Africa.

Date: December 2000

I hereby declare that the material incorporated into this thesis is my own original and unaided work except where specific reference is made by name or in the form of a numbered reference. The work contained herein has not been submitted for a degree at any other university.

Signed:

Cedric Worthmann

With all my love, to my *Mom*, *Dad*, and *Liesl*, for all their inspiration, support, sacrifices and encouragement.

#### Abstract

During the past two decades, Quality of Supply has become a serious problem for Variable Speed Drives in the industrial and commercial sectors. Quality of Supply problems can trip Variable Speed Drives, which results in loss of production, which is a significant problem in the paper and pulp industry. Researchers have proposed that Quality of Supply problems can be minimised in-house, using controlled front end rectifiers (boost rectifier), to maintain a regulated DC link voltage in the Variable Speed Drive configuration, as most faults are created by a varying supply voltage.

This thesis extends the work performed on boost rectifiers by investigating the feasibility of replacing the classical controllers with a Continual Online Trained Artificial Neural Network current controller. The approach adopted in this thesis was to evaluate and extend the work previously performed on conventional boost rectifier current controllers and Continual Online Trained Artificial Neural Network current controlled inverter, at the University of Natal. During this evaluation, the respective controller shortcomings were identified and addressed. Thereafter the Continual Online Trained Artificial Neural Network current controller was modified, according to the control requirements of the boost rectifier, and used as a replacement for the conventional current controller in the boost rectifier system. Finally, the Continual Online Trained Artificial Neural Network current controller was evaluated to assess its viability as a current controller for a boost rectifier.

The concept of implementing the real-time Continual Online Trained Artificial Neural Network current controller using a DSP (Digital Signal Processor) was described, along with the main features and practical limitations of existing commercial DSP's. It is shown that at the time of writing of this thesis, the commercially available DSP's are not powerful enough to implement the Continual Online Trained Artificial Neural Network current controller. However this thesis also shows that it is feasible to implement the real-time controller on the newly released TMS320C67 DSP card.

# Acknowledgments

The work presented in this thesis was carried out under the supervision of Mr G Diana of the Department of Electrical Engineering, University of Natal, Durban. I wish to thank Mr Diana for his advice, guidance and support.

#### I also wish to thank:

- My family and friends for their support throughout my University career;

- My colleges Messrs M.L. Walker, A. Stylo, B. van Blerk, T. Rae, B. Burton, M.

Pillay, Ganesh K. Venayagamoorthy, R. Hariparsad;

- The technical staff, particularly Messrs A. Roos, A. G. M. Munnick, G. Loubser and

A. Stengel for their assistance;

- The Foundation for Research and development (FRD) in South Africa and the University of Natal, for providing financial support.

- Mrs Fiona Higginson, Dr Derrick Hoch and Professor Broadhurst for providing courage during a trying time.

- Eskom TESP.

- And last, my colleagues from Eskom Electro-technology Test and Demonstration

Center, Westmead, for all their support and encouragement.

# **Table of Contents**

| Abstract        |                                                                | i    |

|-----------------|----------------------------------------------------------------|------|

| Acknowledgm     | ents                                                           | ii   |

| Table of Conte  | ents                                                           | iii  |

| List of Figures | and Tables                                                     | viii |

| List of Symbol  | ls and Abbreviations                                           | xv   |

| CHAPTER 1       | INTRODUCTION                                                   |      |

| 1.1             | General                                                        | 1.1  |

| 1.2             | Thesis Layout                                                  | 1.4  |

| 1.3             | New Formulations                                               | 1.6  |

| 1.4             | Publications                                                   | 1.6  |

| CHAPTER 2       | OVERVIEW OF PREVIOUS WORK                                      |      |

| 2.1             | Introduction                                                   | 2.1  |

| 2.2             | Quality of Supply                                              | 2.4  |

| 2.3             | Conventional Rectifiers and their Shortcomings                 | 2.5  |

|                 | 2.3.1 Phase-controlled Thyristor Rectifier                     | 2.5  |

|                 | 2.3.2 Three-phase Diode Rectifier                              | 2.6  |

| 2.4             | Improved Rectifier Topologies and Control Schemes              | 2.7  |

| 2.5             | Chathury's Conventional Boost Rectifier Controller             | 2.11 |

| 2.6             | COT ANN based IM Current Controller                            | 2.15 |

|                 | 2.6.1 The Basic Principles of System Identification using ANNs | 2.15 |

|           |        |                                                             | page iv    |

|-----------|--------|-------------------------------------------------------------|------------|

|           | 2.6.2  | Burton's adaptive current control law                       | 2.16       |

| 2.7       | Summ   | nary                                                        | 2.20       |

| CHAPTER 3 |        | SIMULATION OF A CONTINUOUSLY ONLI                           | NE TRAINED |

|           |        | ARTIFICIAL NEURAL NETWORK CONTROLLEI                        | ) VOLTAGE- |

|           |        | SOURCE INVERTER FED SCIM DRIVE                              |            |

| 3.1       | Introd | luction                                                     | 3.1        |

| 3.2       |        | ED Simulation of Power Conversion Systems                   | 3.2        |

| 3.3       |        | igation of a basic COT ANN Controlled VSI fed SCIM          | 3.2        |

| 3.3       |        | ble Speed Drive                                             | 3.5        |

| 3.4       |        | igation of the performance of a COT ANN Applied to a        | 5.5        |

| 5.4       |        | ed SCIM Variable Speed Drive                                | 3.13       |

| 3.5       | Summ   |                                                             | 3.38       |

| 3.3       | Summ   | ialy                                                        | 5.50       |

| CHAPTER 4 |        | INVESTIGATION OF A CONTINUOUSLY ONLI                        | NE TRAINED |

|           |        | ARTIFICIAL NEURAL NETWORK CURRENT CONT                      | ROLLER FOR |

|           |        | A BOOST RECTIFIER SYSTEM                                    |            |

| 4.1       | Introd | luction                                                     | 4.1        |

| 4.2       |        | m Outline                                                   | 4.2        |

| 1.2       | 4.2.1  | COT ANN Conventions                                         | 4.2        |

|           | 4.2.2  | Mains Synchronization                                       | 4.7        |

|           | 4.2.3  | DC link Voltage Controller                                  | 4.9        |

| 4.3       |        | tigation of a COT ANN Current Controller for a Boost Rectif |            |

|           | 4.3.1  | ANN Learning Rate                                           | 4.20       |

|           | 4.3.2  |                                                             | 4.22       |

|           | 4.3.3  | · ·                                                         | 4.25       |

|           |        | 0                                                           | 23         |

|           |        | page                                                                | v      |

|-----------|--------|---------------------------------------------------------------------|--------|

|           | 4.3.4  | ANN Sampling Frequency                                              | 4.26   |

|           | 4.3.5  | Alpha/Beta Current and Voltage Feedback Terms                       | 4.29   |

|           | 4.3.6  | Proportional Gain                                                   | 4.31   |

| 4.4       | Summ   | ary                                                                 | 4.40   |

| CHAPTER 5 | 5      | FEASIBILITY OF USING A DSP-BASED COT ANN CU                         | JRRENT |

|           |        | CONTROLLER                                                          |        |

| 5.1       | Introd | untion                                                              | 5.1    |

| 5.2       |        |                                                                     | 5.2    |

| 3.2       | 5.2.1  | Ssor Requirements                                                   |        |

|           |        | Transputer versus ADC64 DSP card                                    | 5.2    |

|           | 5.2.2  | Controller Computational Requirements                               | 5.3    |

|           | 5.2.2  | Proposed DSP solution                                               | 5.11   |

| 5.3       | Summ   | ary                                                                 | 5.14   |

| CHAPTER 6 | 5      | CONCLUSION AND RECOMMENDATIONS                                      |        |

| 6.1       | Gener  | ral                                                                 | 6.1    |

| 6.2       | Sugge  | estions for Further Work                                            | 6.3    |

| APPENDIX  | A      | DERIVATION OF EQUATIONS                                             |        |

| A.1       | Faust  | ions for the Boost Rectifier Power Conversion System in             |        |

| 24.1      | -      | oordinates                                                          | A.1    |

|           | A.1.1  |                                                                     | A.1    |

| A.2       |        | risation of the dynamic power balance equation during rectification | A.1    |

|           |        |                                                                     |        |

| A.3       |        | MAX model of the Boost Rectifier                                    | A.6    |

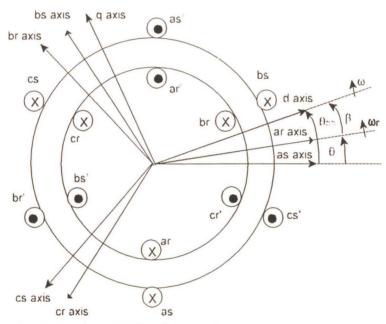

|           | A.3.1  | Continuous Time Electrical Model of the Induction Motor             | A.7    |

|          | -       | page vi                                                           |      |

|----------|---------|-------------------------------------------------------------------|------|

|          | A.3.2   | Derivation of the Electrical NARMAX Model of the Boost rectifier  | A.13 |

|          | A.3.3   | Root-locus Angle and Magnitude Conditions                         | A.18 |

| APPENDIX | В       | SIMULATION CODE LISTING                                           |      |

| B.1      | Artific | ial Neural Network model for SCIM drive                           | B.1  |

| B.2      | Simpli  | fied Induction motor model                                        | B.13 |

| B.3      | Artific | ial Neural Network model                                          | B.17 |

| B.4      | PWM     | Hanning Model                                                     | B.29 |

| B.5      | Induct  | ion motor model                                                   | B.38 |

| B.6      | Three-  | -Phase Sinusoidal Source Model                                    | B.43 |

| B.7      | User N  | Model for Neural Network Current Controller for a Boost Rectifier | B.46 |

| C 1      | PWM     | Control Block Function                                            | C.1  |

| C.1      |         | Control Block Function                                            | C.1  |

|          | C.1.1   |                                                                   | C.1  |

| 0.0      |         | PWM Control Block C-source code                                   | C.5  |

| C.2      |         | Current Controller Block Function                                 | C.13 |

|          |         | ANN Current Controller Block Include Code                         | C.13 |

|          | C.2.2   | ANN Current Controller Block C-source code                        | C.19 |

| APPENDIX | D       | BOOST RECTIFIER HARDWARE PROFILE                                  |      |

|          |         |                                                                   |      |

| D.1      | Overv   | riew                                                              | D.1  |

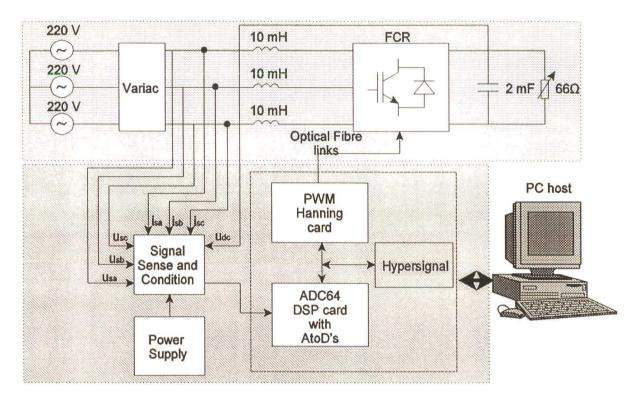

| D.2      |         | cal System Structure                                              | D.2  |

| D.3      | The P   | ower Circuit                                                      | D.3  |

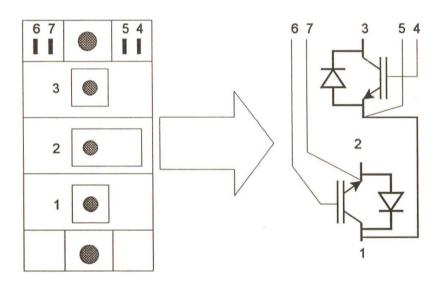

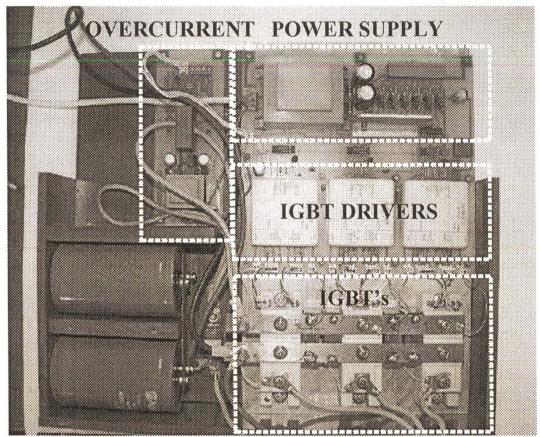

|          | D.3.1   | The Insulated Gate Bipolar Transistor Boost Rectifier             | D.4  |

Table of Contents

|          |        |                                           | page vii |

|----------|--------|-------------------------------------------|----------|

|          | D.3.2  | Electrical Load                           | D.5      |

|          | D.3.3  | Three-phase Supply                        | D.6      |

| D.4      | The Co | ontrol Hardware                           | D.6      |

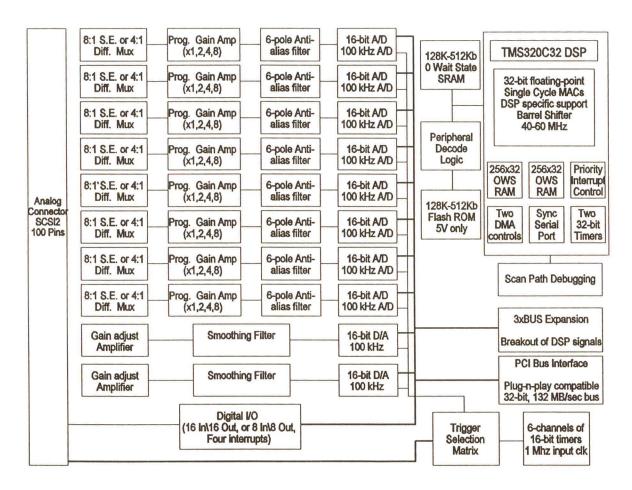

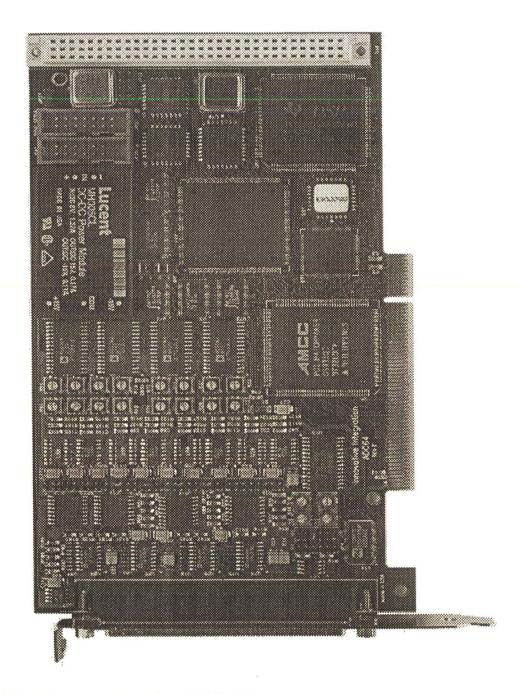

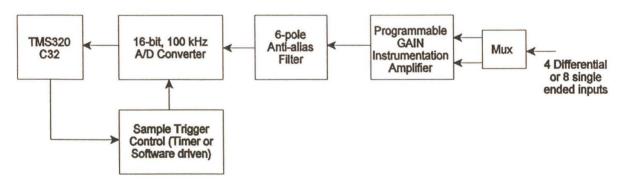

|          | D.4.1  | ADC64 Digital Signal Processing Card      | D.6      |

|          | D.4.2  | Hanning PWM Interface Card                | D.12     |

|          | D.4.3  | Optical Fibre Interface Circuitry         | D.18     |

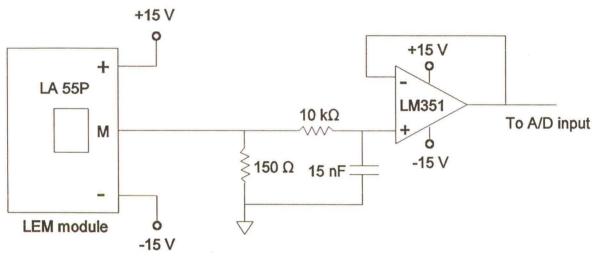

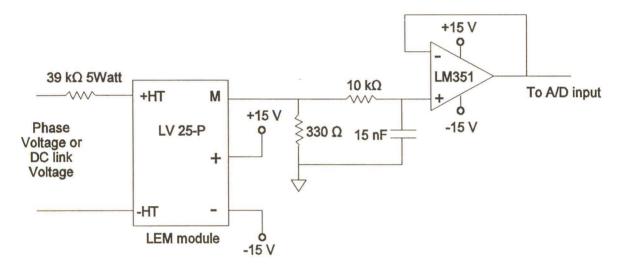

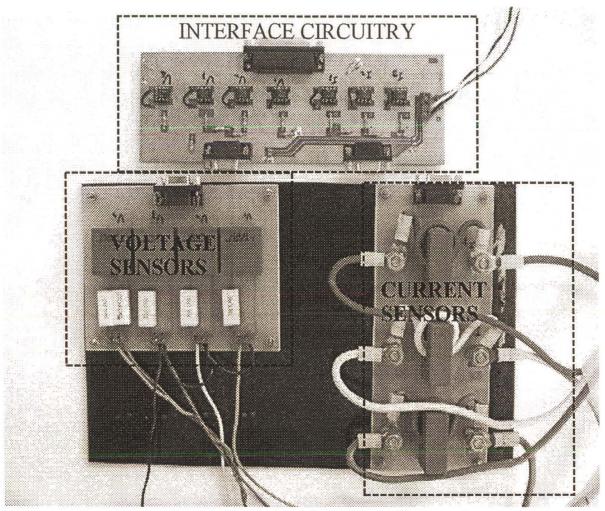

|          | D.4.4  | Signal Sensing and Conditioning Circuitry | D.20     |

|          |        |                                           |          |

| REFERENC | ES     |                                           | R.1      |

# List of Figures and Tables

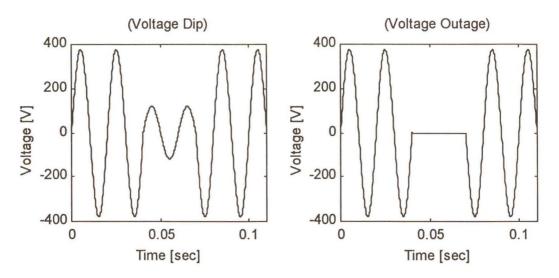

| Fig. 1.1 Supply voltage dip or outage                                                                            | 1.2  |

|------------------------------------------------------------------------------------------------------------------|------|

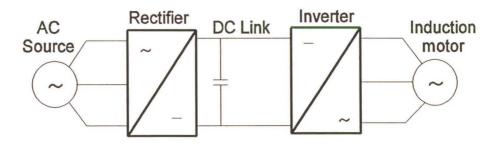

| Fig. 1.2 Voltage-Sourced Inverter                                                                                | 1.2  |

|                                                                                                                  |      |

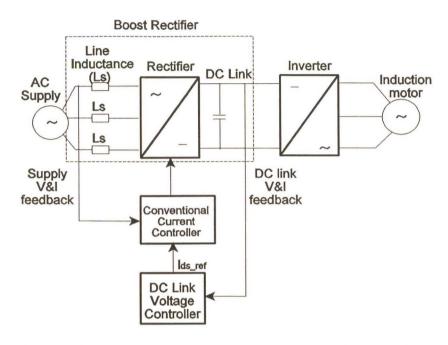

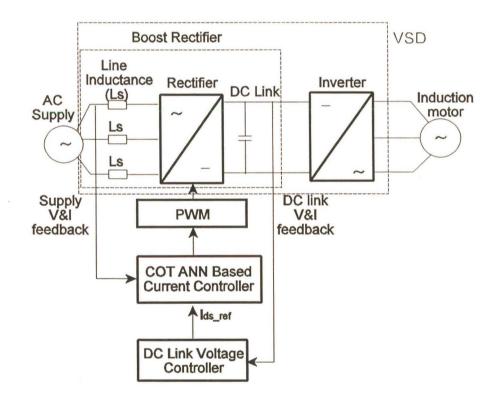

| Fig. 2.1 Conventional controller configuration used to control a boost rectifier                                 | 2.2  |

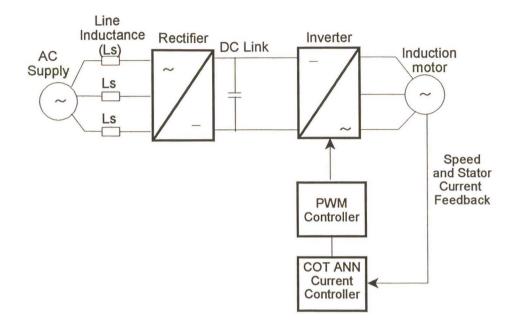

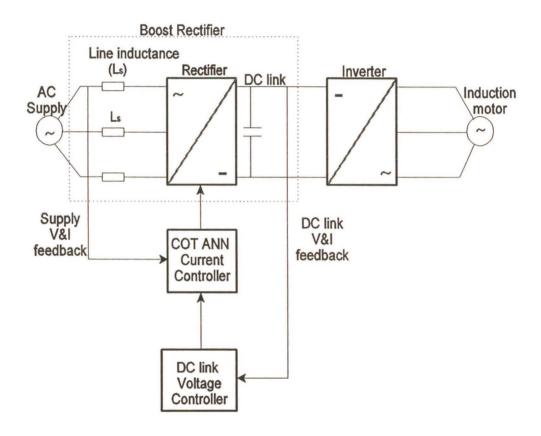

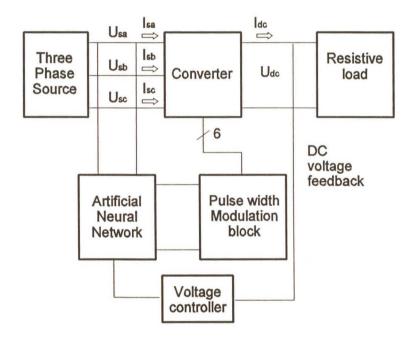

| Fig. 2.2 COT ANN controlled VSI fed SCIM drive                                                                   | 2.3  |

| Fig. 2.3 Proposed boost rectifier control loops                                                                  | 2.3  |

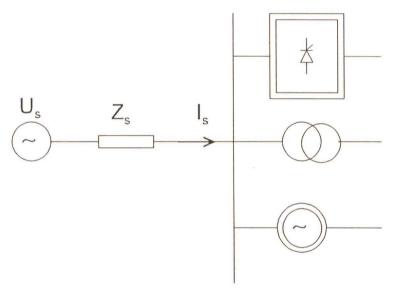

| Fig. 2.4 Simplified power network                                                                                | 2.4  |

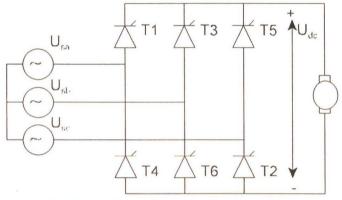

| Fig. 2.5 Three-phase thyristor rectifier                                                                         | 2.5  |

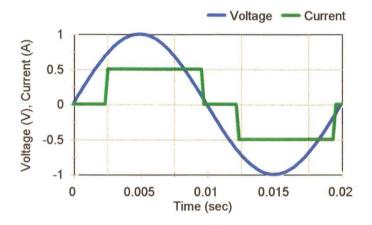

| Fig. 2.6 Typical phase A operating voltage and current at $\alpha$ =15°                                          | 2.6  |

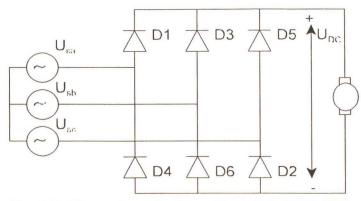

| Fig. 2.7 Three-phase diode rectifier                                                                             | 2.7  |

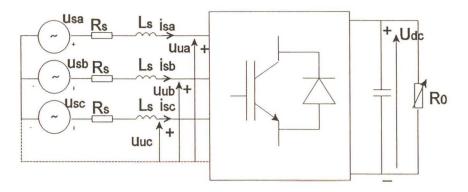

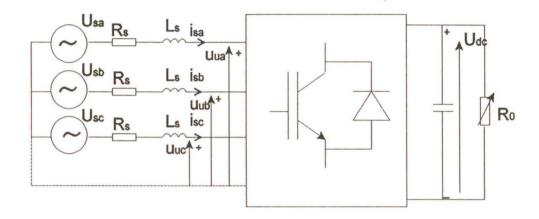

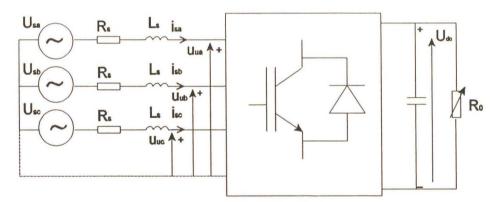

| Fig. 2.8 Boost rectifier configuration                                                                           | 2.11 |

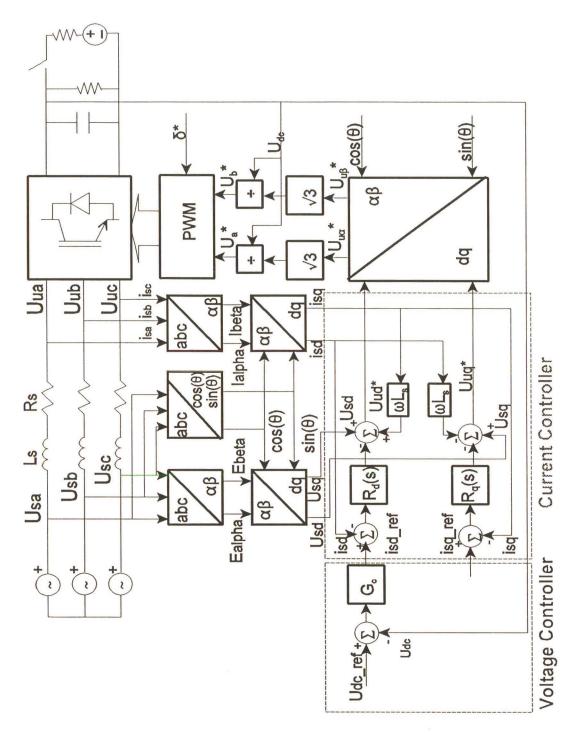

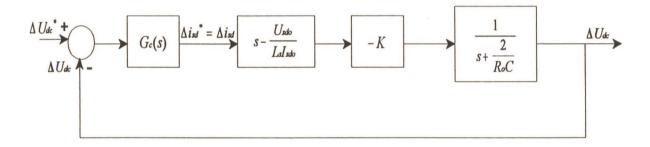

| Fig. 2.9 Chathury's boost rectifier current and voltage controller                                               | 2.13 |

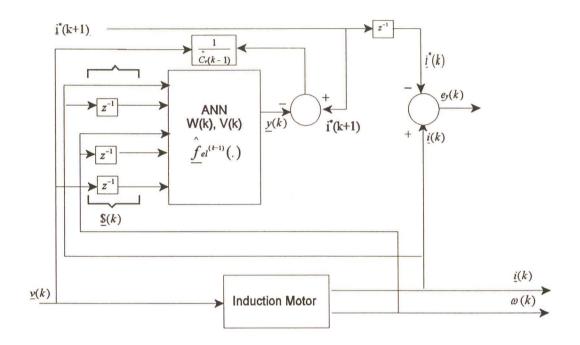

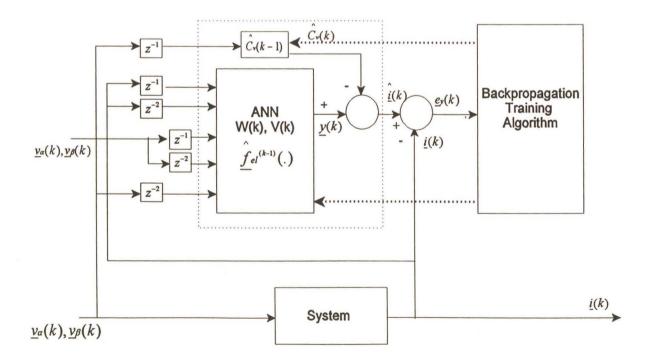

| Fig. 2.10 Block diagram of the current control law Eqn. (2.11)                                                   | 2.19 |

|                                                                                                                  |      |

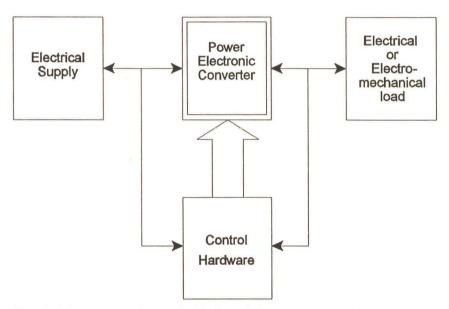

| Fig. 3.1 Structure of a typical industrial power conversion system                                               | 3.2  |

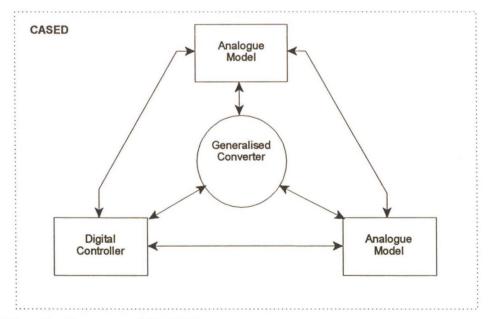

| Fig. 3.2 Structure of CASED                                                                                      | 3.3  |

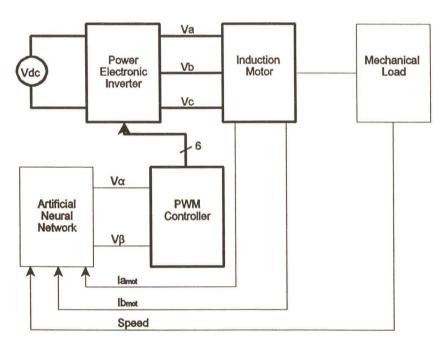

| Fig. 3.3 Basic COT ANN controlled power conversion system                                                        | 3.6  |

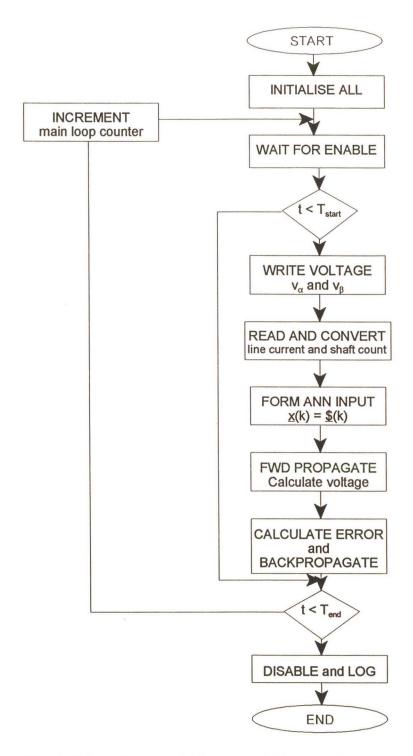

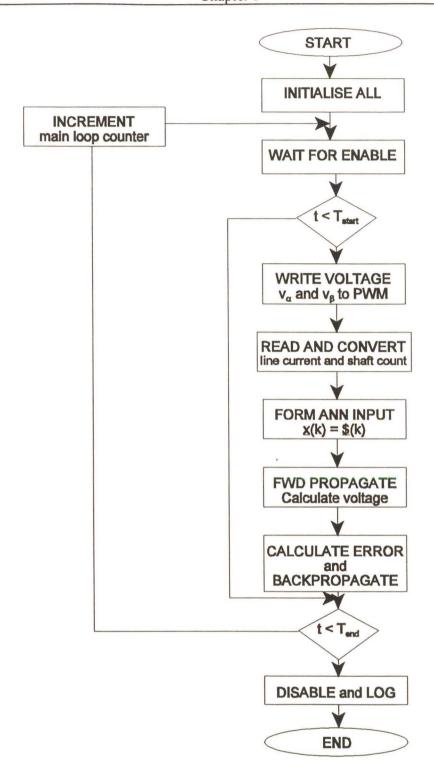

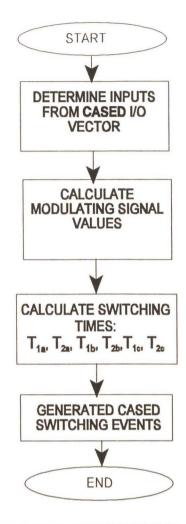

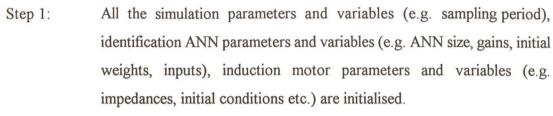

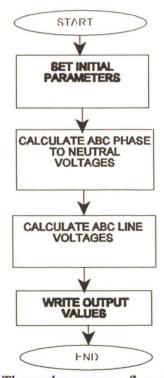

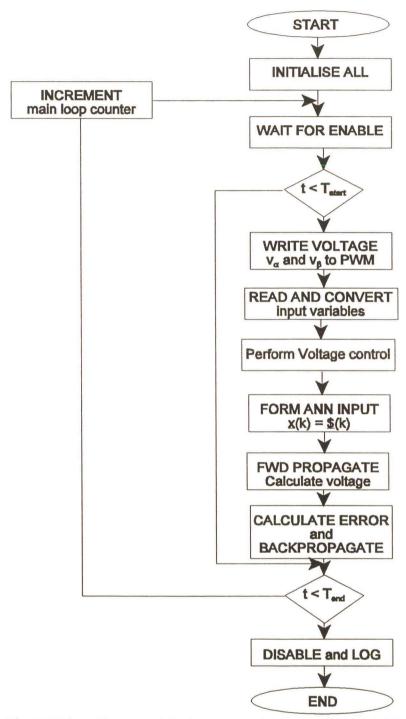

| Fig. 3.4 Flow diagram of COT ANN CASED module                                                                    | 3.7  |

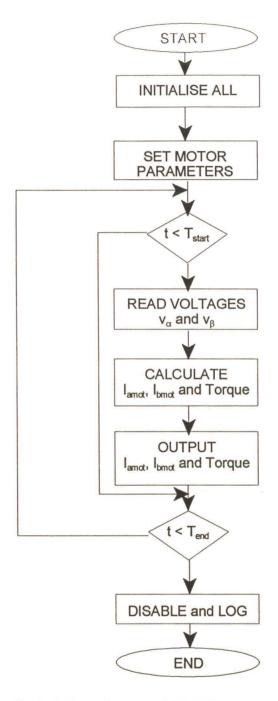

| Fig. 3.5 Flow diagram of CASED induction motor module                                                            | 3.9  |

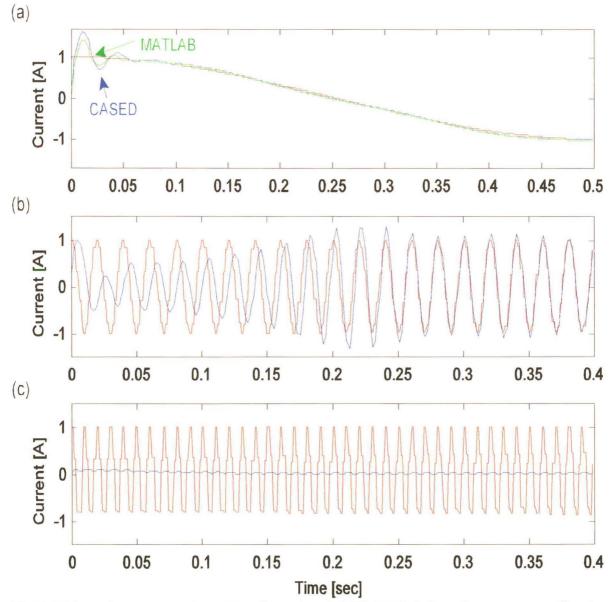

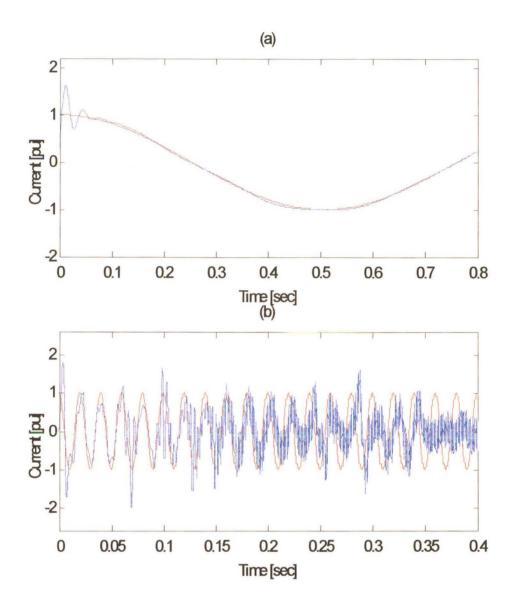

| Fig. 3.6 Phase A motor supply current ( $I_{a\_supply}$ ) and COT ANN alpha reference current                    |      |

| $(I_{\alpha,m})$ , with a sampling rate of 500 Hz, learning rate of 0.1 pu, $c_v$ of 1.5 pu, and                 |      |

| no pretraining at stator frequencies of (a) 1 Hz (CASED and MATLAB results),                                     |      |

| (b) 50 Hz (CASED) and (c) 100 Hz (CASED) respectively.                                                           | 3.11 |

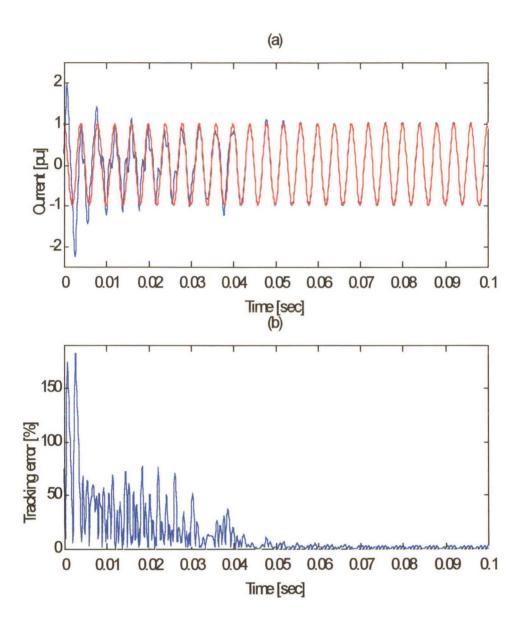

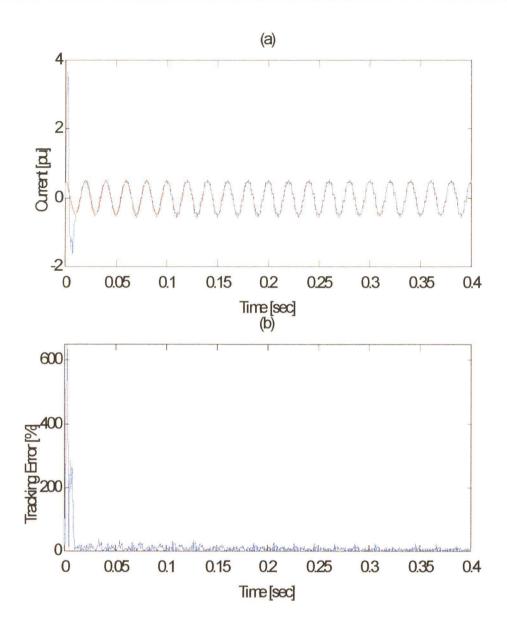

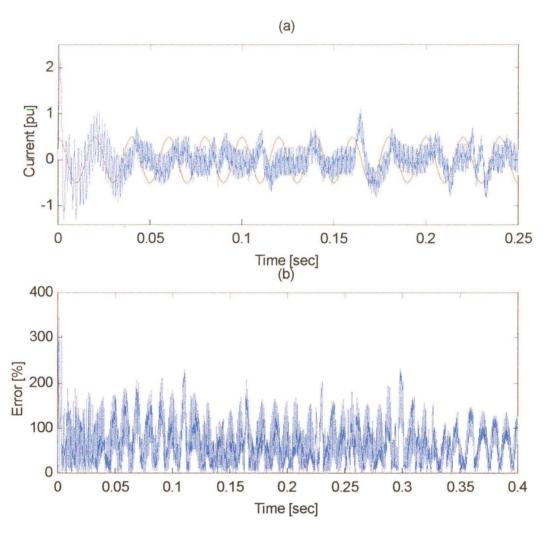

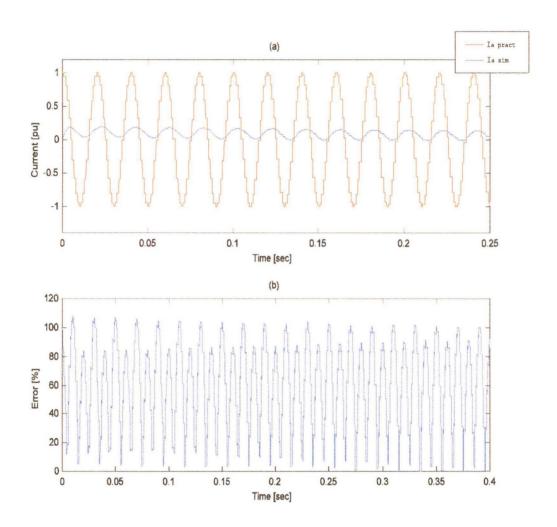

| Fig. 3.7 (a) Phase A motor current ( $I_{a\_supph}$ ) and COT ANN alpha reference current ( $I_{\alpha\_ref}$ ), |      |

| with a sampling frequency of 10 kHz and learning rate of 0.1 pu, (b) Current                                     |      |

| tracking error                                                                                                   | 3.12 |

|                                                                                                                  |      |

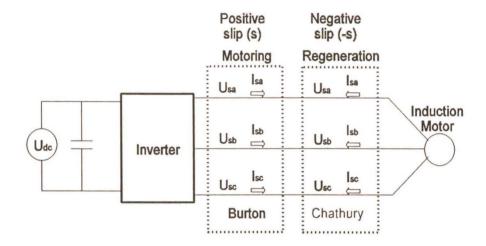

| Fig. 3.8 Block diagram of a COT ANN controlled SCIM drive                                              | 3.13 |

|--------------------------------------------------------------------------------------------------------|------|

| Fig. 3.9 Flow diagram of COT ANN CASED module for control of a VSI fed SCIM VSD                        | 3.15 |

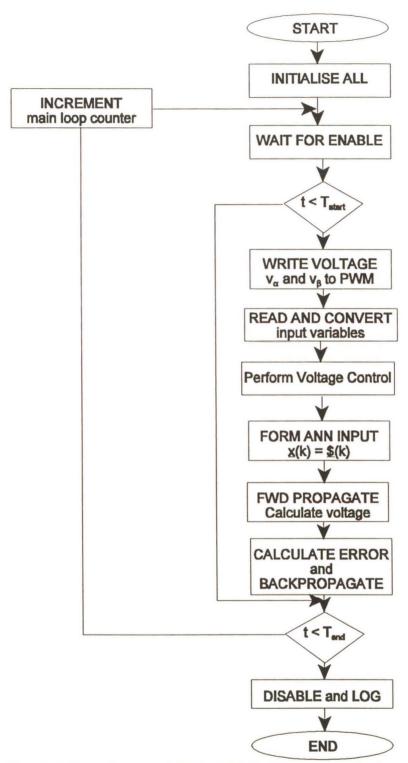

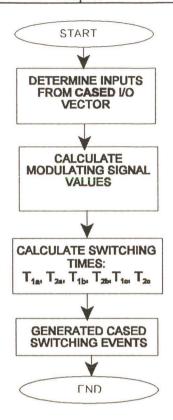

| Fig. 3.10 Flow diagram of PWM CASED module                                                             | 3.17 |

| Fig. 3.11 Phase A motor supply current $(I_{a\_supply})$ and COT ANN alpha reference current           |      |

| $(I_{\alpha,ref})$ , with sampling frequency of 10 kHz, learning rate of 0.5 pu and $C_v$ of 1.5 pu,   |      |

| at motor frequencies of (a) 1 Hz and (b) 50 Hz respectively                                            | 3.19 |

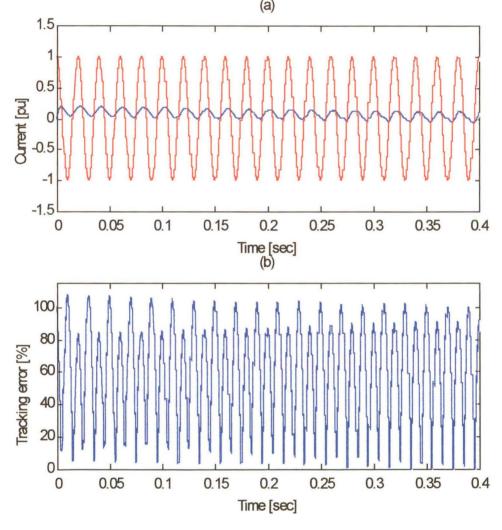

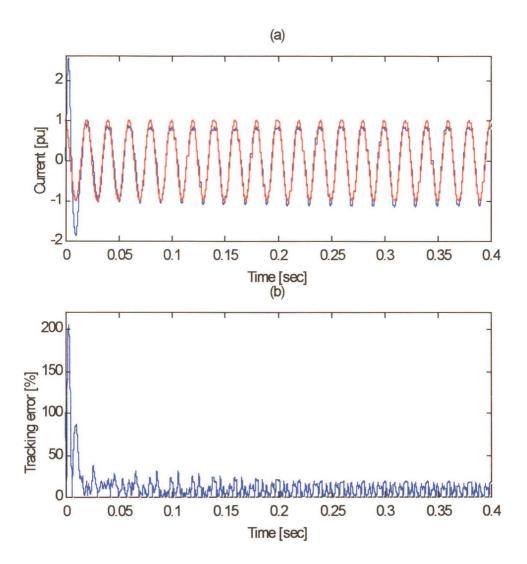

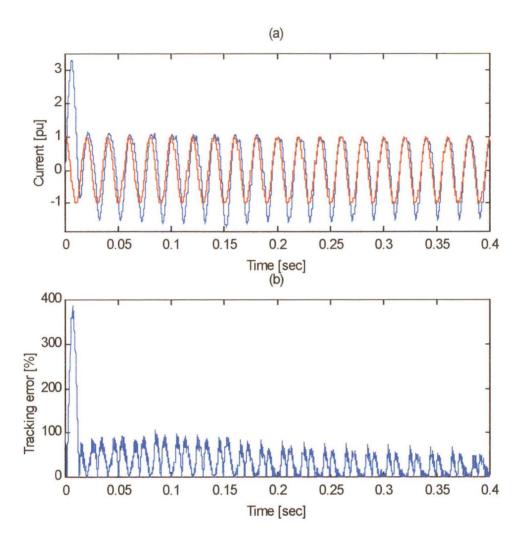

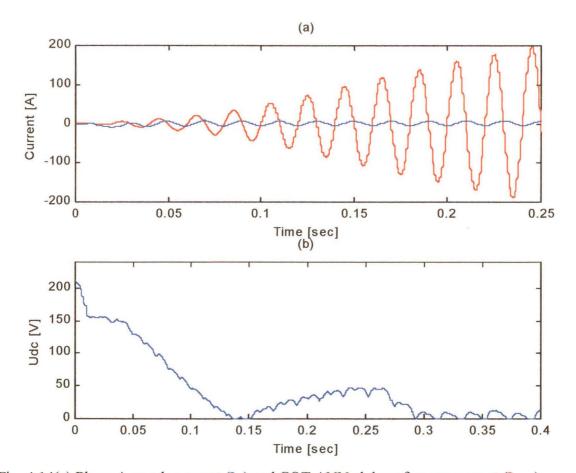

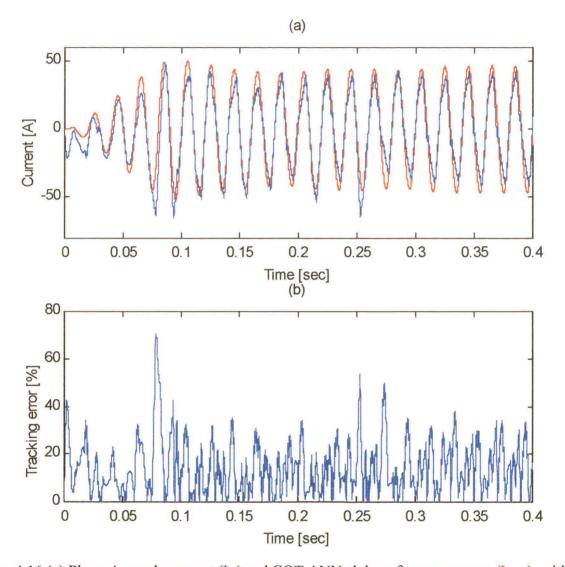

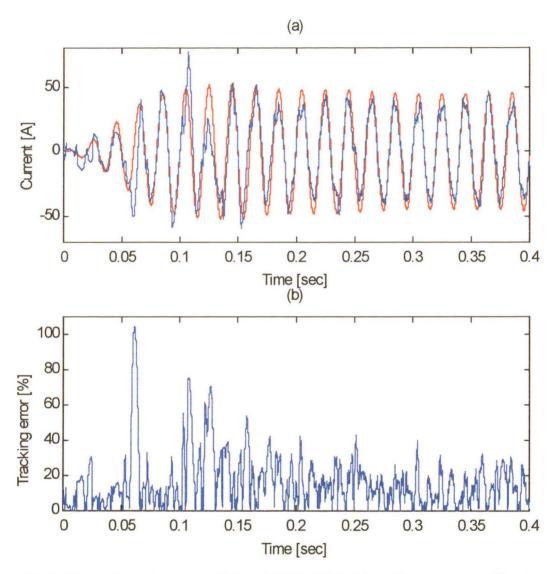

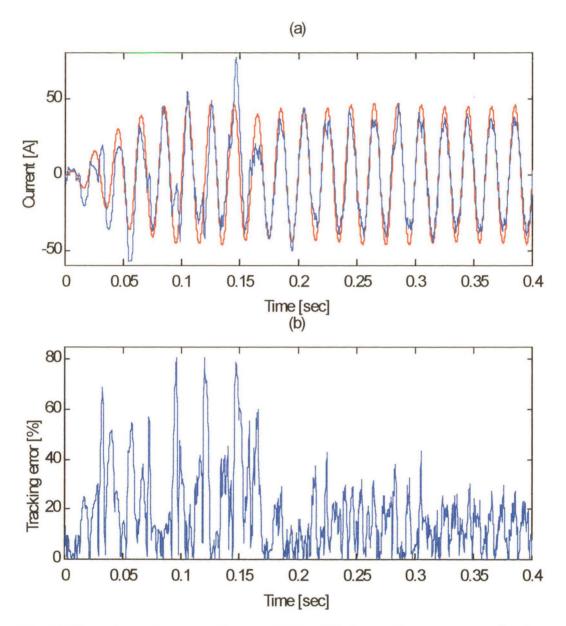

| Fig 3.12 (a) Phase A motor supply current ( $I_{a\_supply}$ ) and COT ANN alpha reference current      |      |

| $(I_{\alpha, ref})$ , with K = 0.1 pu, sampling frequency of 1 kHz, learning rate of 0.01 pu, stato    | r    |

| frequency of 50 Hz and stator current magnitude of 1 pu,                                               |      |

| (b) Current tracking error                                                                             | 3.20 |

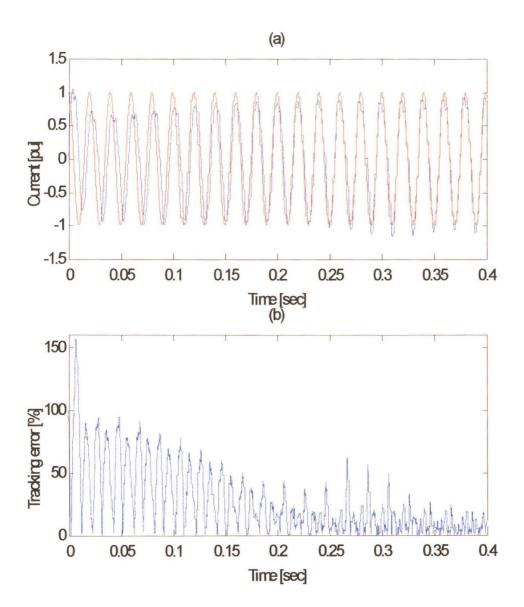

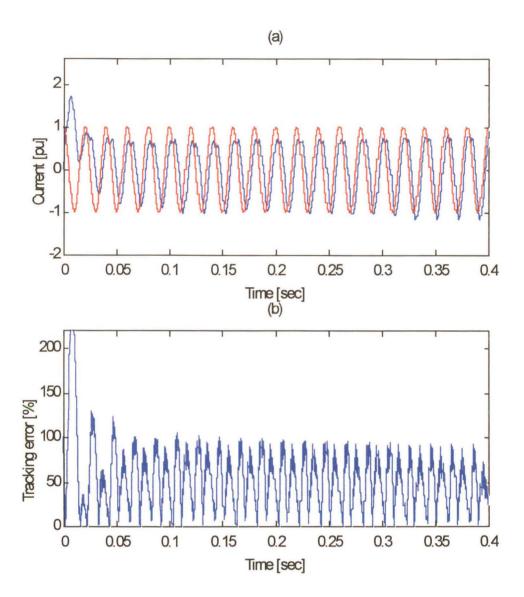

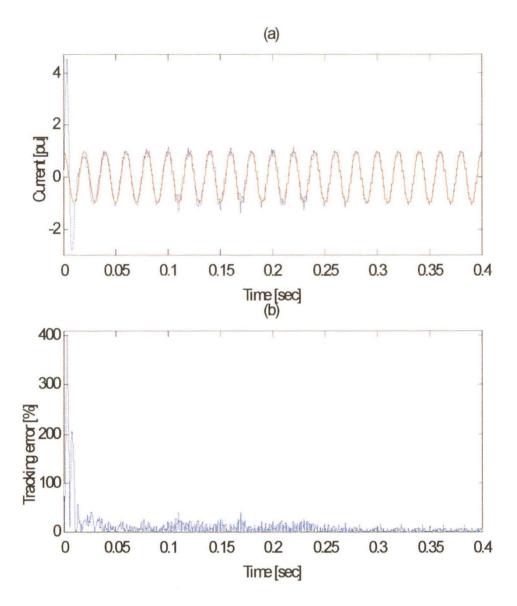

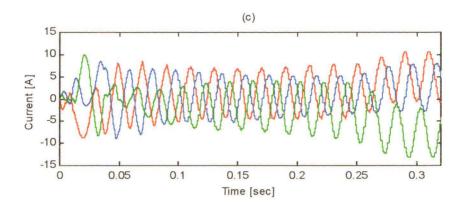

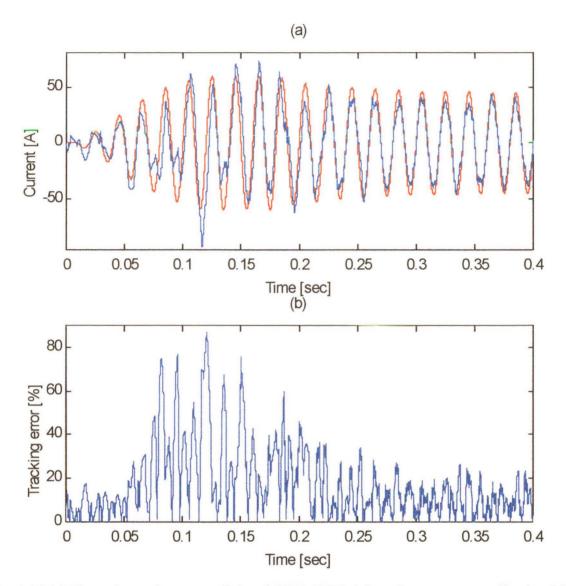

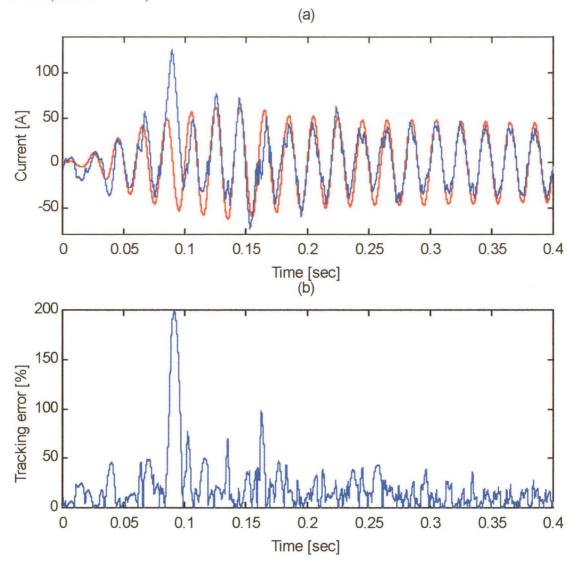

| Fig 3.13 (a) Phase A motor supply current (I <sub>a_supply</sub> ) and COT ANN alpha reference current |      |

| $(I_{\alpha,ref})$ , with K = 0.1 pu, sampling frequency of 5 kHz, learning rate of 0.01 pu, state     | or   |

| frequency of 50 Hz and stator current magnitude of 1 pu,                                               |      |

| (b) Current tracking error                                                                             | 3.21 |

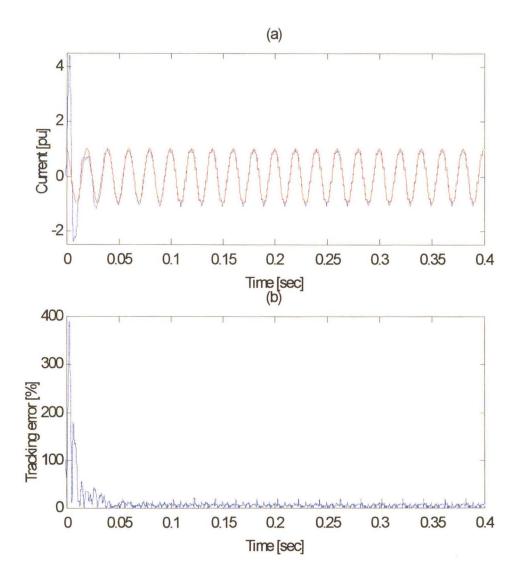

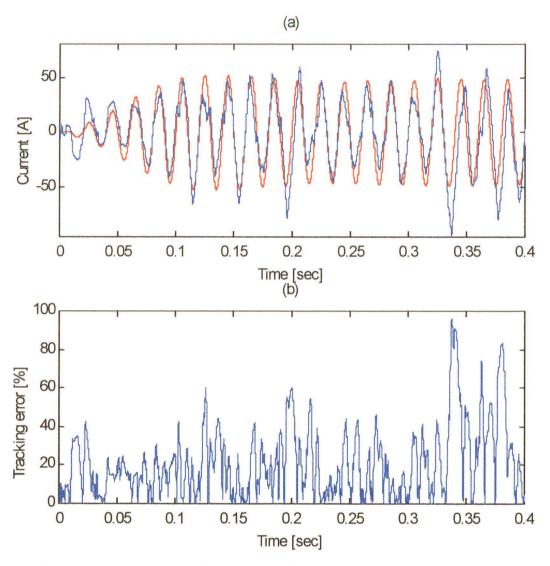

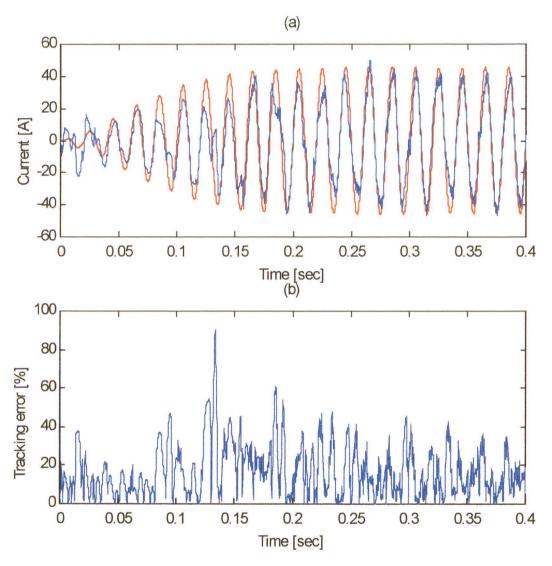

| Fig 3.14 (a) Phase A motor supply current ( $I_{a\_supply}$ ) and COT ANN alpha reference current      |      |

| $(I_{\alpha,rel})$ , with K = 0.1 pu, sampling frequency of 10 kHz, learning rate of 0.01 pu,          |      |

| stator frequency of 50Hz and stator current magnitude of 1 pu,                                         |      |

| (b) Current tracking error                                                                             | 3.22 |

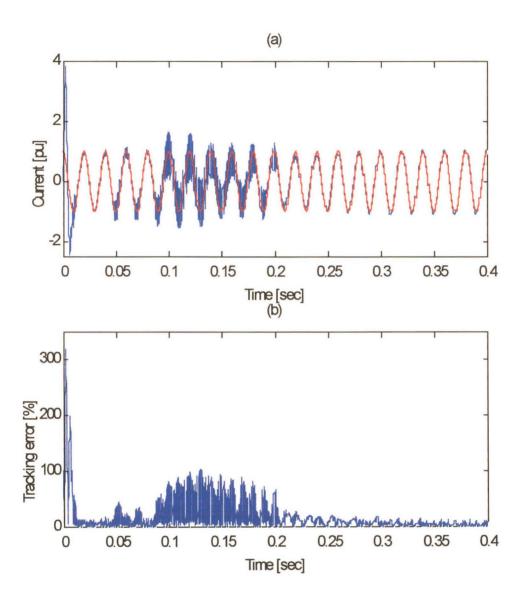

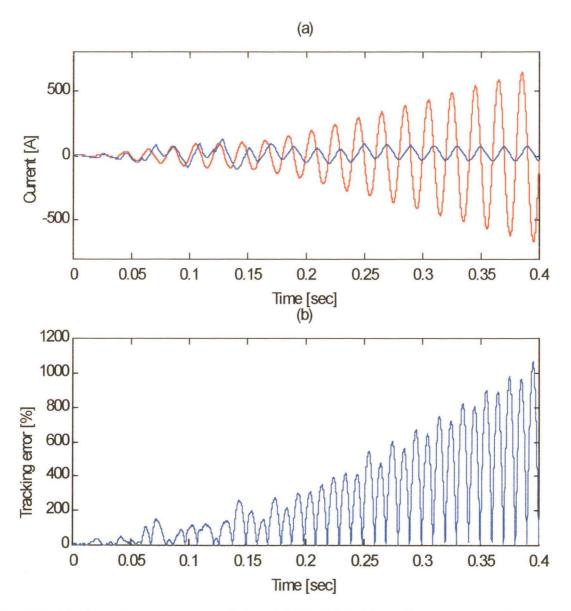

| Fig 3.15 (a) Phase A motor supply current ( $I_{a\_supply}$ ) and COT ANN alpha reference current      |      |

| $(I_{\alpha,ref})$ , with K = 0.6 pu, sampling frequency of 1 kHz, learning rate of 0.01 pu, state     | or   |

| frequency of 50 Hz and stator current magnitude of 1 pu,                                               |      |

| (b) Current tracking error                                                                             | 3.24 |

| Fig 3.16 (a) Phase A motor supply current $(I_{a\_supply})$ and COT ANN alpha reference current        |      |

| $(I_{\alpha,mf})$ , with K = 0.6 pu, sampling frequency of 5 kHz, learning rate of 0.01 pu, state      | tor  |

| frequency of 50Hz and stator current magnitude of 1 pu,                                                |      |

| (b) Current tracking error                                                                             | 3.25 |

|                                                                                                        |      |

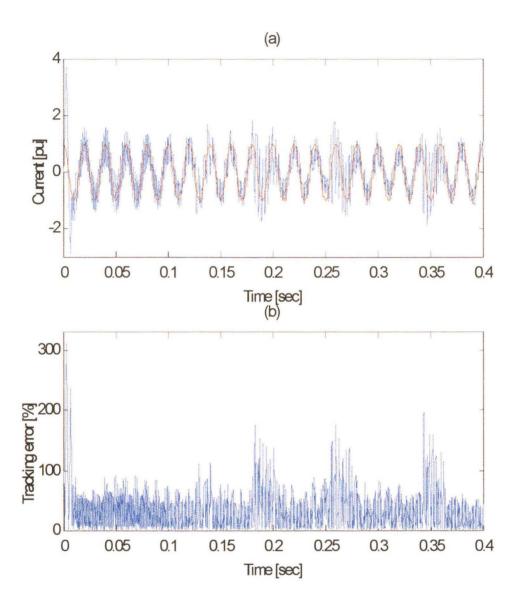

| Fig 3.17 (a) Phase A motor supply current (Ia_supply) and COT ANN alpha reference current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| $(I_{\alpha,rei})$ , with K = 0.6 pu, sampling frequency of 10 kHz, learning rate of 0.01 pu,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| stator frequency of 50Hz and stator current magnitude of 1 pu,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| (b) Current tracking error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.26 |

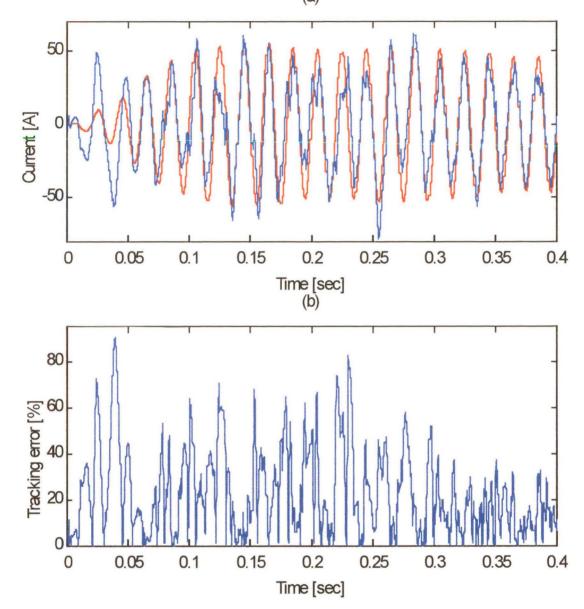

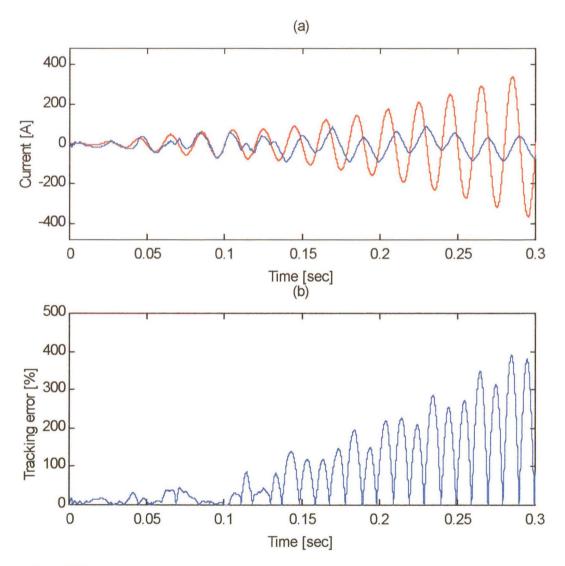

| Fig 3.18 (a) Phase A motor supply current ( $I_{a\_supply}$ ) and COT ANN alpha reference current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| $(I_{\alpha_{-}, ref})$ , with K = 0.9 pu, sampling frequency of 1 kHz, learning rate of 0.01 pu, state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ır   |

| frequency of 50 Hz and stator current magnitude of 1 pu,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| (b) Current tracking error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.28 |

| Fig 3.19 (a) Phase A motor supply current ( $I_{a\_supply}$ ) and COT ANN alpha reference current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| $(I_{\alpha,ref})$ , with K = 0.9 pu, sampling frequency of 5 kHz, learning rate of 0.01 pu, state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ır   |

| frequency of 50 Hz and stator current magnitude of 1 pu,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| (b) Current tracking error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.29 |

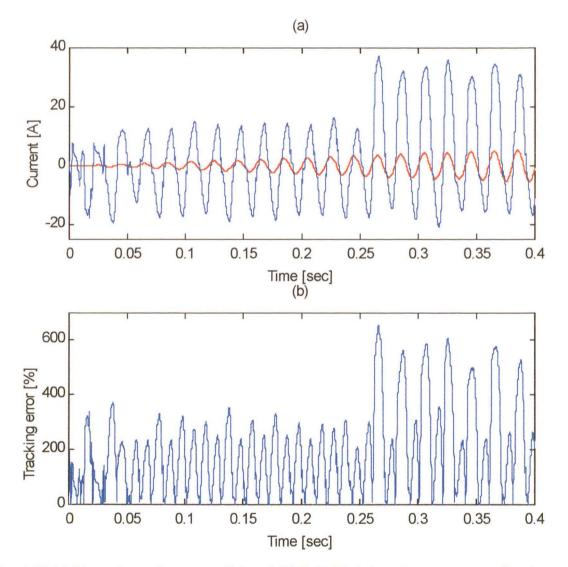

| Fig 3.20 (a) Phase A motor supply current ( $I_{a\_supply}$ ) and COT ANN alpha reference current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| $(I_{\alpha_{\text{res}}})$ , with K = 0.9 pu, sampling frequency of 10 kHz, learning rate of 0.01 pu,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| stator frequency of 50 Hz and stator current magnitude of 1 pu,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| (b) Current tracking error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.30 |

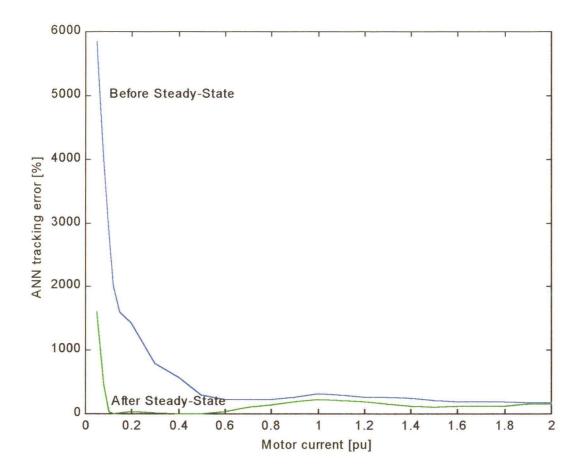

| Fig. 3.21 Current dependence, T <sub>s</sub> =10 kHz, B=0.01 pu, C <sub>v</sub> =0.6 pu, and motor frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| f = 50  Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.32 |

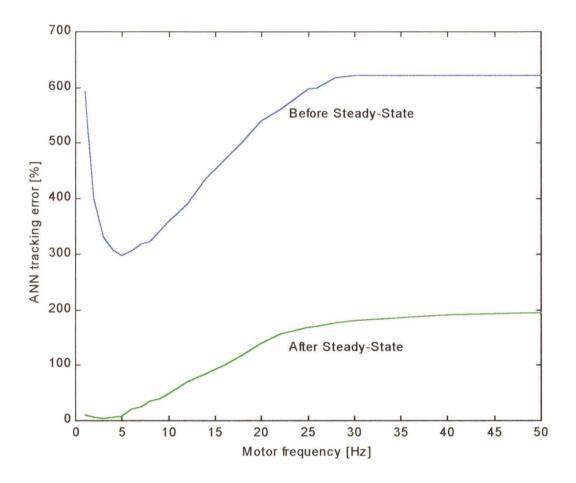

| Fig. 3.22 Motor frequency dependence, $T_s$ =10 kHz, B=0.01 pu, $C_v$ =0.6 pu, and motor current series and the series of the ser | ıt   |

| I=0.5 pu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.33 |

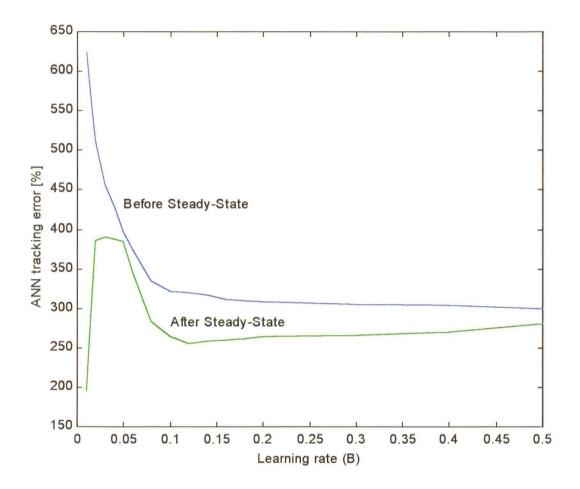

| Fig. 3.23 ANN learning rate dependence, $T_s$ =10 kHz, $C_v$ =0.6 pu, I=0.5 pu and f=50 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.34 |

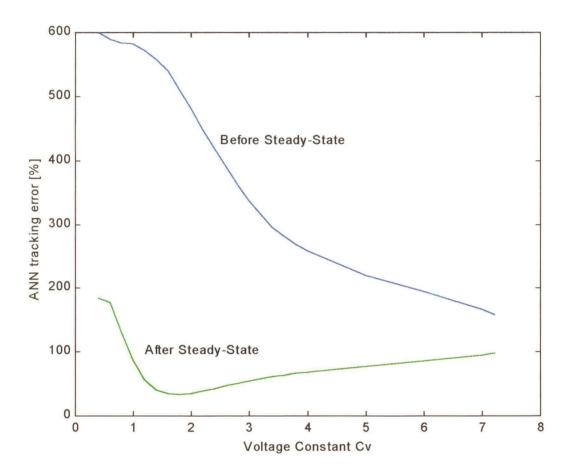

| Fig. 3.24 ANN voltage constant dependence, T <sub>s</sub> =10 kHz, B=0.01 pu, I=0.5 pu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| and f=50 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.35 |

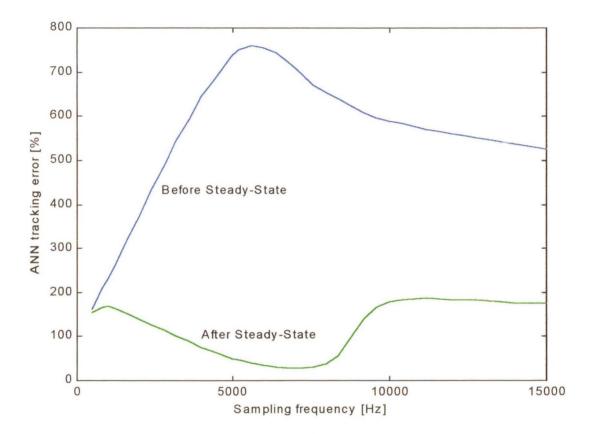

| Fig. 3.25 ANN sampling frequency dependence, Cv=0.6 pu, B=0.01 pu, f=50 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| and I=0.5 pu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.36 |

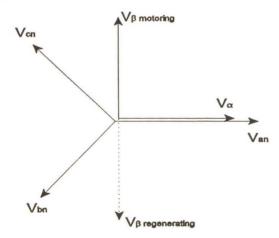

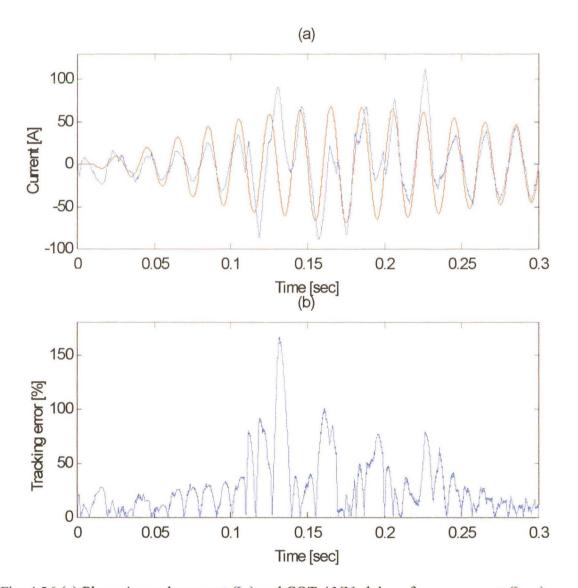

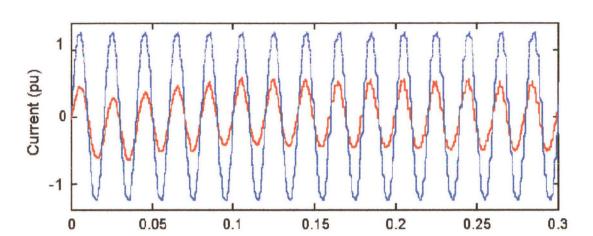

| Fig. 3.26 (a) Phase A motor supply current ( $I_{a\_supply}$ ) and COT ANN alpha reference current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

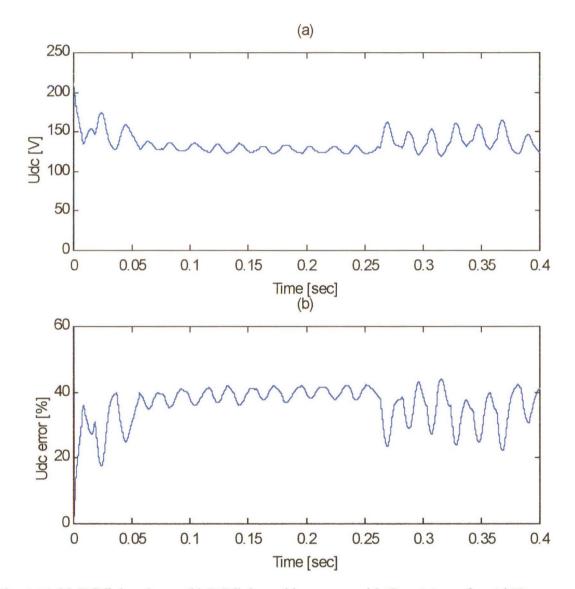

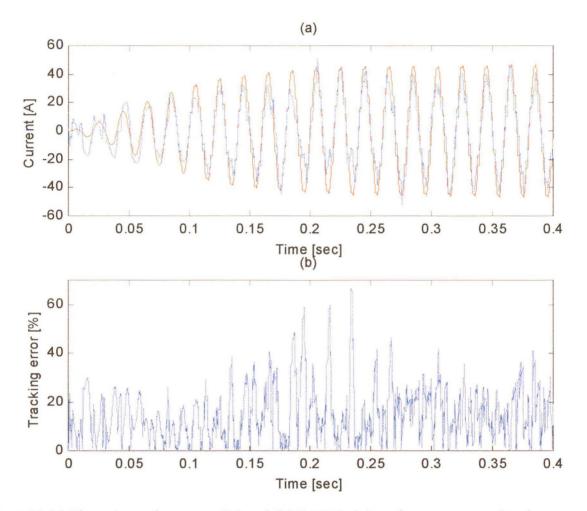

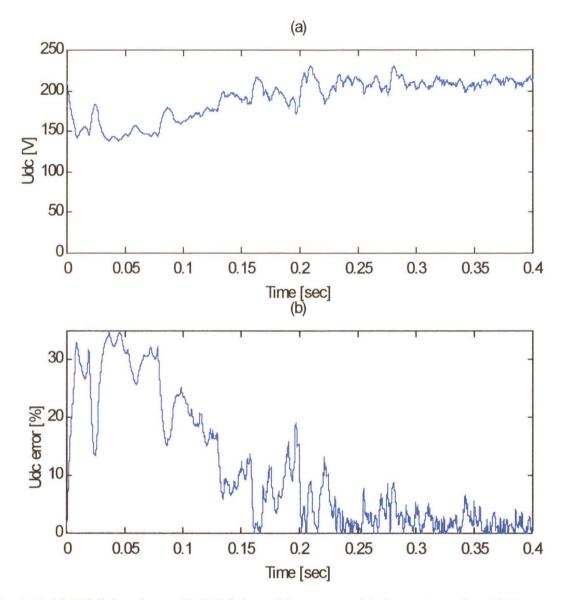

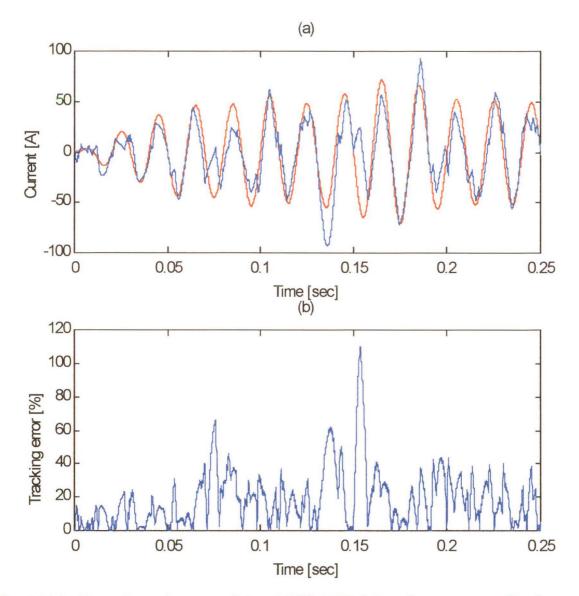

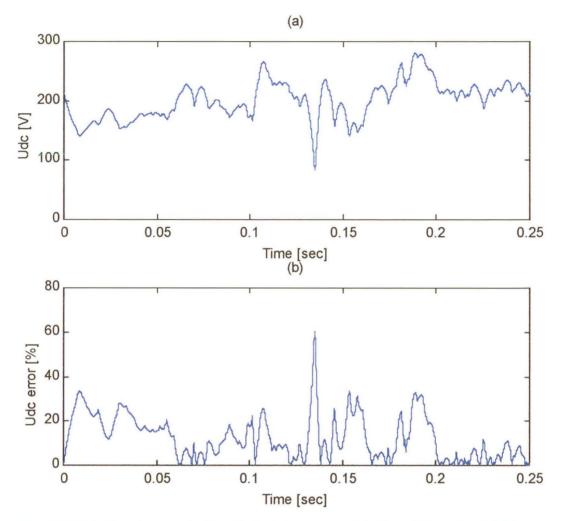

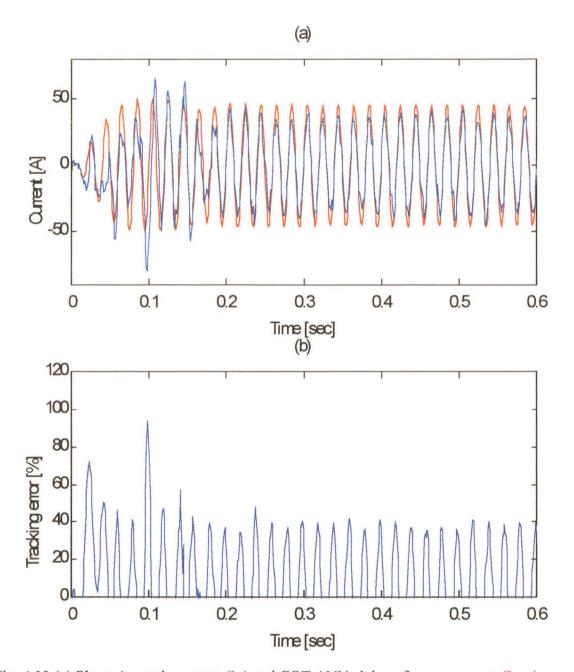

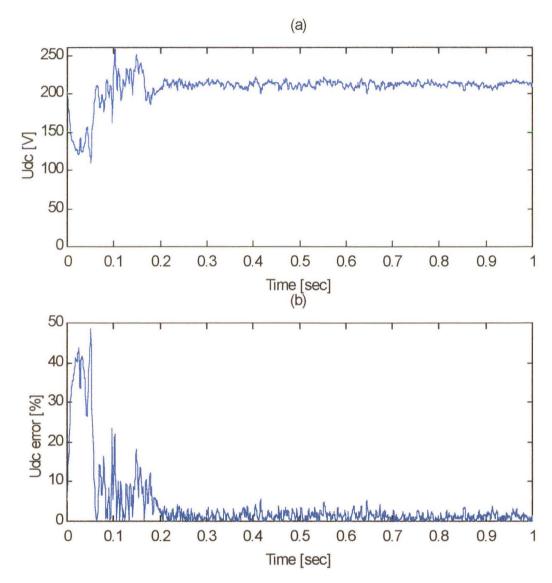

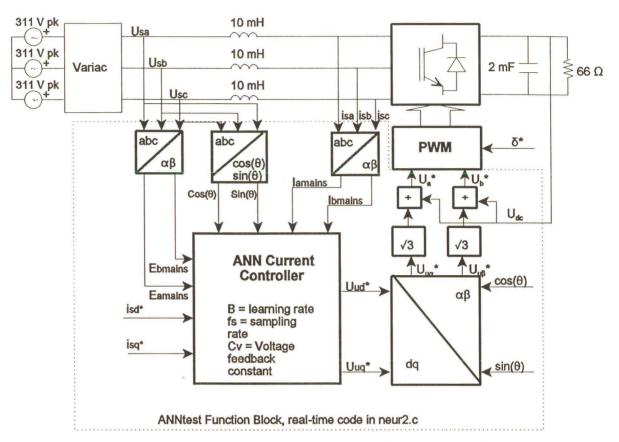

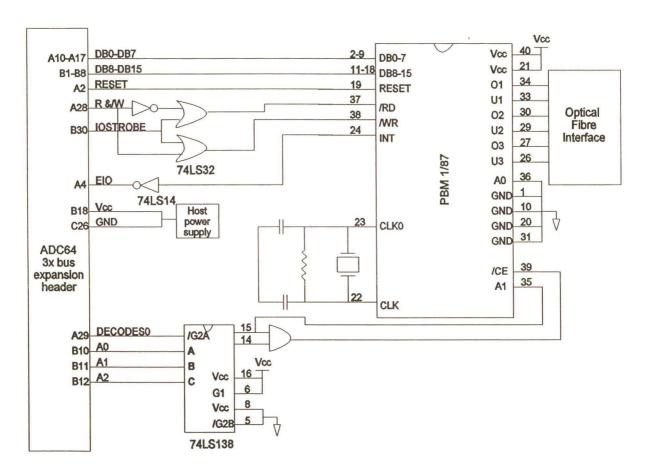

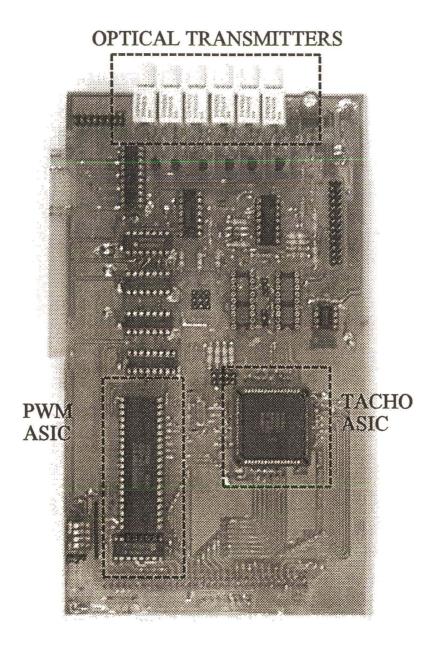

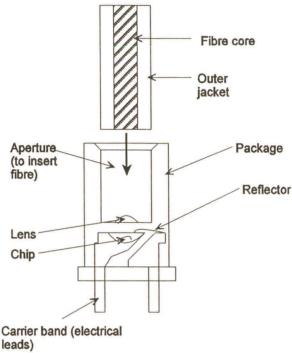

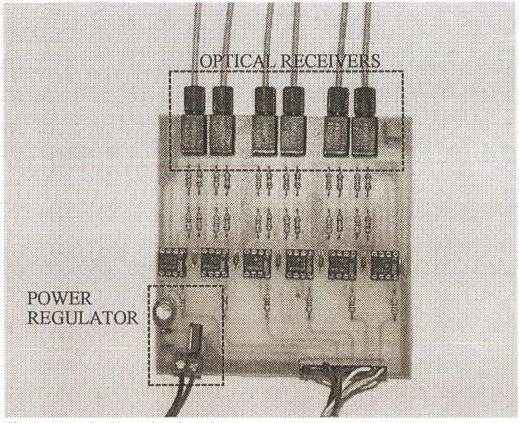

| $(I_{\alpha_{}rof})$ , with K = 0.6 pu, sampling frequency of 8 kHz, learning rate of 0.01 pu,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |