# Impact of different pulse width modulation (PWM) techniques on the performance of a three phase Z-Source inverter (ZSI)

By

Mbulelo Siyabonga Perfect Ngongoma

214502368

A dissertation submitted in partial fulfillment of the requirements for the degree

Of

Master of Science in Electrical Engineering

College of Agriculture, Engineering and Science, University of KwaZulu-

KWAZUL<sub>2019</sub> - NATAL

Supervisor: Dr. A. Saha

# **ABSTRACT**

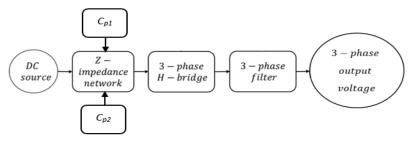

Traditional voltage source inverters (VSIs) have recently advanced to Z-source inverters (ZSIs). A Z-source inverter is a recent topology of DC-AC inverters that was proposed in 2002 by Prof. F. Z. Peng and has taken over from its predecessors; a voltage-source inverter and a current-source inverter [1], [2], [3]. There were two key modifications applied to VSIs to transform them into ZSIs, viz. the inclusion of a link Z-impedance network between a dc-source and the actual inverter stage (topological amendment); as well the inclusion of the ninth operational state, as opposed to only eight zero and active permissible operating states on VSIs, called the shoot-through state (Control scheme amendment) [2].

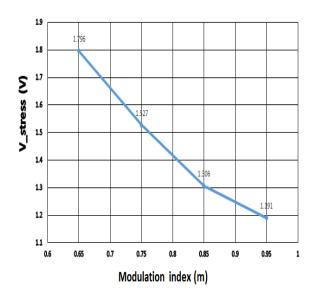

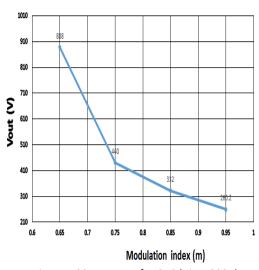

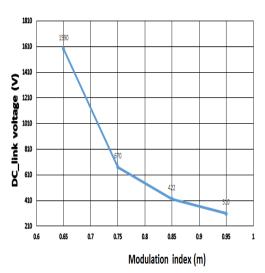

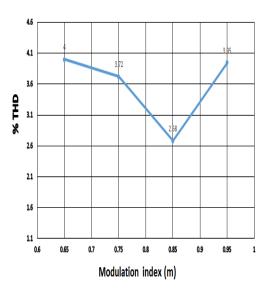

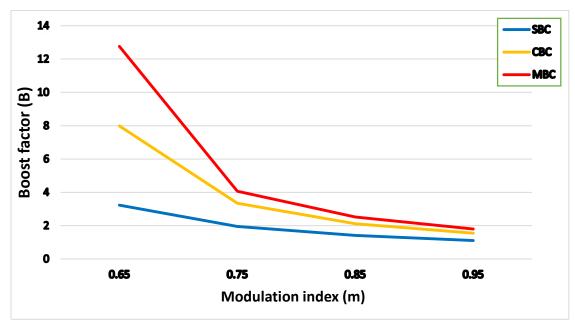

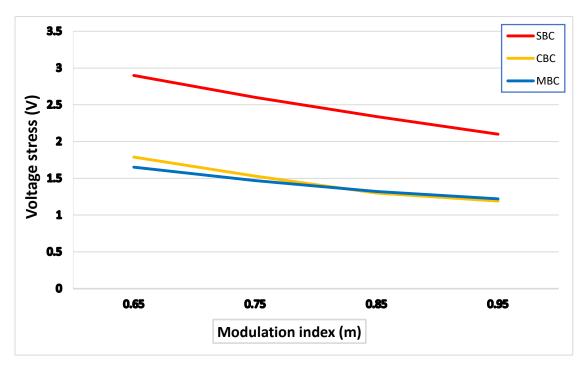

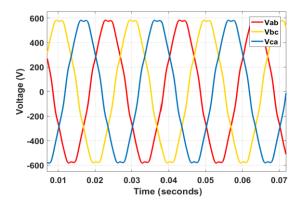

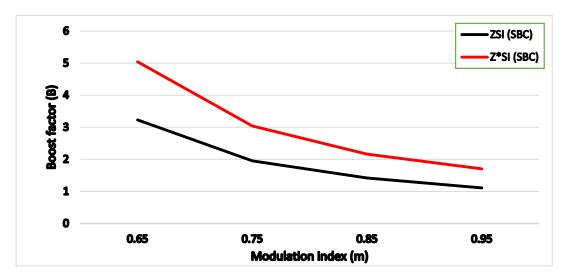

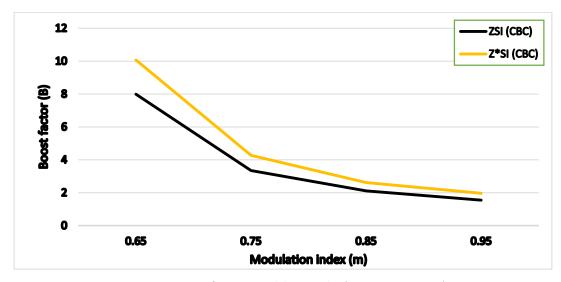

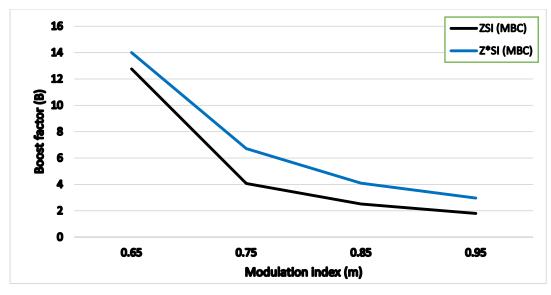

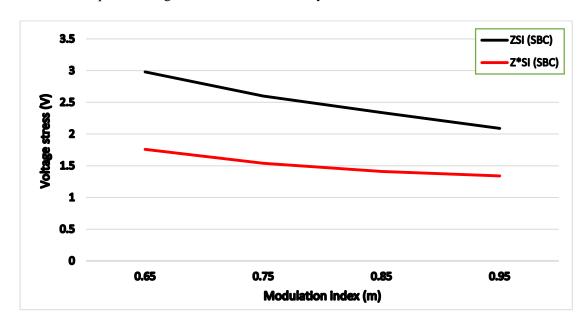

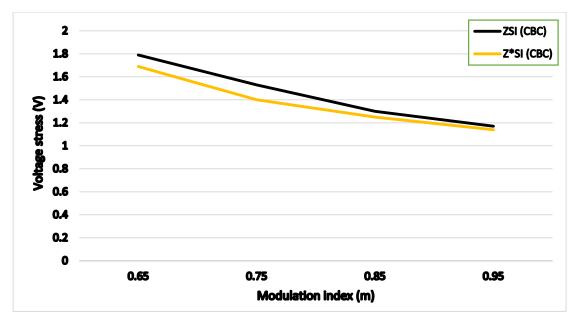

In this dissertation, a detailed design of the ZSI is presented. LCL filter is a choice in this design because it gives superb attenuation of -60 Db/decade to switching frequency opposed to LC and L filters whose attenuation is -40 Db/decade and -20 Db/decade respectively [5]. LCL filters are also light in weight, smaller in size and cheaper than LC and L filters for the same rating. Three pulse width modulation (PWM) techniques viz. simple boost control (SBC), constant boost control (CBC) as well as the maximum boost control (MBC); are developed and applied to a ZSI after-which they are compared with each other for critical performance parameters; traditional sine pulse with modulation (SPWM) is only featured as a reference for the other three PWM control techniques sine it does not boost voltage. The boost factor (B), DC-link voltage (V<sub>dc-link</sub>) and percentage of total harmonics distortion (%THD) are exclusively dependent on the modulation index (m) for all three control techniques. MBC has the highest boost factor and hence the highest DC-link voltage, followed by CBC and SBC coming last; for the same modulation index. MBC has the highest %THD followed by CBC and SBC coming last, for the same modulation index. SBC poses the highest stress on the IGBTs/MOSFETs followed by MBC and CBC coming last; for the same gain [4] [5].

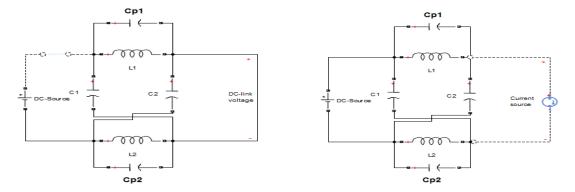

Addition of two parallel capacitors C<sub>p1</sub> and C<sub>p2</sub> across inductors L<sub>1</sub> and L<sub>2</sub> respectively, to form a different topology called a Capacitor-Boosted-Z-Source Inverter (CB-ZSI) has proven to improve the response of this topology relative to a classical ZSI. The boost factor of CB-ZSI is increased by more than 56% at SBC technique, more than 25% at CBC technique and more than 14% at MBC technique on average. Since the gain factor is a linear function of a boost factor with the proportionality constant being the modulation index, the percentage of improvement of gain factors from ZSI to CB-ZSI remains the same as that of boost factors across SBC, CBC and MBC techniques. The voltage stress ratio across the switching devices of a CB-ZSI is reduced by more than 40% at MBC technique, more than 5% at CBC control and increased by 1.7% for MBC PWM control technique on average. %THD for CB-ZSI is reduced by more than 112% for SBC technique, more than 16.8% for CBC and increased by more than 24% for MBC technique on average

In general, CB-ZSI topology shows improve response and hence improved power quality compared to a classical ZSI topology and also proves to be more economical. The rating of switching devices is reduced due to reduced voltage stress posed by a CB-ZSI compared to a ZSI. The ratings of the passive components forming an impedance network are also reduced because a CB-ZSI achieves a large boost factor at a shorter shoot-through time intervals and hence higher modulation index compared to a ZSI.

#### **DECLARATION**

| As the candidate's Supervisor I    | agree to the submiss | ion of this thesis | . The supervisor | must sign |

|------------------------------------|----------------------|--------------------|------------------|-----------|

| all copies after deleting which is | s not applicable     |                    |                  |           |

| Signed: |    |       |    |  |  |  |

|---------|----|-------|----|--|--|--|

|         |    |       |    |  |  |  |

|         | Dr | A Sal | าล |  |  |  |

#### I Mbulelo Siyabonga Perfect Ngongoma declare that

- 1. The research reported in this thesis, except where otherwise indicated, and is my original research.

- 2. This thesis has not been submitted for any degree or examination at any other university.

- 3. This thesis does not contain other persons' data, pictures, graphs or other information, unless specifically acknowledged as being sourced from other persons.

- 4. This thesis does not contain other persons' writing, unless specifically acknowledged as being sourced from other researchers. Where other written sources have been quoted, then:

- a) Their words have been re-written but the general information attributed to them has been referenced

- b) Where their exact words have been used, then their writing has been placed in italics and inside quotation marks, and referenced.

- 5. This thesis does not contain text, graphics or tables copied and pasted from the Internet, unless specifically acknowledged, and the source being detailed in the thesis and in the References sections.

| Signed: |  |  |  |  |

|---------|--|--|--|--|

|         |  |  |  |  |

Mbulelo Siyabonga Perfect Ngongoma

# **ACKNOWLEDGEMENTS**

The author would like to thank all parties involved for their contribution especially the following individuals and organisations:

- Dr. A Saha

- Miss Bonakele Monica Ngongoma

- Mr. Themba Alois Ngongoma

- Mr. Nathi Peter-john Mlaba

- Miss Zodwa Makhaye

- Mvelo Sfundo Msani

- Miss Khululiwe Delight Gumede

- Ngangezwe High School

- South African Breweries (SAB)

- Assmang Catoridge Works (ACRW)

- Family and friends

# **TABLE OF CONTENTS**

| ABSTRA  | ACT                                                        | i    |

|---------|------------------------------------------------------------|------|

| DECLA   | RATION                                                     | ii   |

| ACKNO   | WLEDGEMENTS                                                | iii  |

| LIST OF | FIGURES                                                    | vi   |

| LIST OF | TABLES                                                     | viii |

| LIST OF | ABBREVIATIONS                                              | ix   |

| 1. INT  | RODUCTION                                                  | 1    |

| 1.1.    | Introduction of the research work undertaken               | 1    |

| 1.2.    | Motivation                                                 | 1    |

| 1.3.    | Research question                                          | 4    |

| 1.4.    | Background                                                 | 5    |

| 1.5.    | Thesis aims and objective                                  | 8    |

| 1.6.    | Thesis organisation                                        | 9    |

| 2. LIT  | ERATURE REVIEW                                             | 11   |

| 2.1.    | A voltage-source inverter (VSI)                            | 11   |

| 2.2.    | A current-source inverter (CSI)                            |      |

| 2.3.    | A classical three-phase Z-source inverter topology         |      |

| 2.3.    | 1. A general overview                                      | 14   |

| 2.3.    | 2. The circuit analysis                                    | 16   |

| 2.4.    | The output filter design                                   | 17   |

| 2.4.    | 1. LC-filter                                               | 17   |

| 2.4.    |                                                            |      |

| 2.5.    | The PWM control techniques                                 | 19   |

| 2.5.    | 1. Simple Boost Control                                    | 20   |

| 2.5.    | 2. Constant Boost Control                                  | 21   |

| 2.5.    | 3. Maximum Boost Control                                   | 22   |

| 2.6.    | Conclusion                                                 | 23   |

| 3. ME   | THODOLOGY                                                  | 24   |

| 3.1.    | Literature review                                          | 25   |

| 3.2.    | Design of a three-phase Z-source inverter circuit          | 25   |

| 3.3.    | Design of PWM control techniques                           |      |

| 3.4.    | Selection of a simulation tool                             |      |

| 3.5.    | Results of a ZSI and discussion                            | 30   |

| 3.6.    | Development of a CB-Z-Source Inverter performance criteria | 31   |

| 3         | .7.   | Desi | gn of a CB-Z-Source Inverter                                  | .31  |

|-----------|-------|------|---------------------------------------------------------------|------|

| 3         | .8.   | Resi | ults of a CB-Z-Source Inverter and discussion                 | .32  |

| 3         | .9.   | Con  | clusion                                                       | .32  |

| 4.        | SIM   | ULA  | TION AND RESULTS OF DIFFERENT PWM CONTROL TECHNIQUES          | .33  |

| 4         | .1.   | Basi | c ZSI design                                                  | .33  |

|           | 4.1.1 | 1.   | Inductor design                                               | .33  |

|           | 4.1.2 | 2.   | Capacitor design.                                             | .34  |

|           | 4.1.3 | 3.   | Filter design                                                 | .34  |

|           | 4.1.4 | 4.   | Selection of switching devices and a diode                    | .35  |

| 4         | .2.   | PWI  | M control schemes                                             | .36  |

|           | 4.2.1 | 1.   | Sine pulse width modulation (SPWM)                            | .36  |

|           | 4.2.2 | 2.   | Simple boost pulse width modulation technique (SBC)           | .43  |

|           | 4.2.3 | 3.   | Constant boost PWM technique (CBC)                            | .49  |

|           | 4.2.4 | 1.   | Maximum boost PWM technique                                   | .55  |

| 5.<br>ZSI |       |      | ED THREE-PHASE CAPACITOR BOOSTED-Z-SOURCE INVERTER(CB-<br>DGY |      |

| 5         | .1.   | Con  | parison of SBC, CBC and MBC critical parameters for a ZSI     | .65  |

| 5         | .4.   | The  | proposed CB-ZSI development                                   | .67  |

|           | 5.4.1 | 1.   | Circuit analysis on different modes of operation              | .67  |

|           | 5.4.2 | 2.   | Results and analysis                                          | .69  |

| 6.        | CON   | NCLU | JSION                                                         | .78  |

| 6         | 5.1.  | Sum  | mary and conclusion on the study's objectives                 | .78  |

| 6         | 5.2.  | Futu | re work considerations                                        | . 79 |

| 7.        | REF   | ERE  | NCES                                                          | .80  |

| 8.        | APP   | END  | DICES                                                         | .82  |

# LIST OF FIGURES

| Figure 1.1: PV-cell connected to a ZSI [4]                           | 2  |

|----------------------------------------------------------------------|----|

| Figure 1.2: Wind turbine connected to a ZSI [6]                      | 2  |

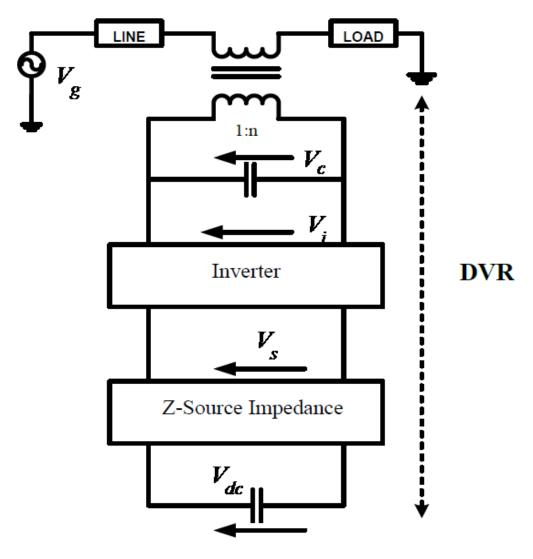

| Figure 1.3: ZSI based UPS system [7]                                 | 3  |

| Figure 1.4: ZSI based DVR system [9]                                 | 4  |

| Figure 1.5: A switched inductor Z-source inverter [10]               |    |

| Figure 1.6: An LCCT-ZSI [13]                                         |    |

| Figure 1.7: An LCCT-qZSI [13]                                        |    |

| Figure 1.8: A DIDO-ZSI circuit diagram [17]                          |    |

| Figure 2.1: A traditional VSI [8]                                    |    |

| Figure 2.2: A traditional CSI [19]                                   |    |

| Figure 2.3: The basic ZSI circuit [6]                                |    |

| Figure 2.4: The ZSI in non-shoot-through state (mode 1 and 2) [3]    |    |

| Figure 2.5: The ZSI in shoot-through state (mode 3) [3]              |    |

| Figure 2.6: An LC filter [22]                                        |    |

| Figure 2.7: An LCL filter [20]                                       |    |

| Figure 2.8: With series damping resistor [21]                        |    |

| Figure 2.10: Simple boost control waveforms                          |    |

| Figure 2.11: Constant boost control waveforms                        |    |

| Figure 2.12: Maximum boost control waveforms                         |    |

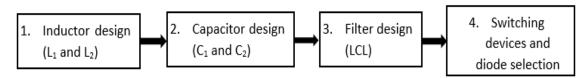

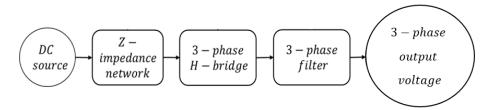

| Figure 3.1: Z-source inverter design block diagram                   |    |

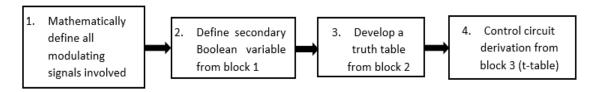

| Figure 3.2: PWM control technique design block diagram               |    |

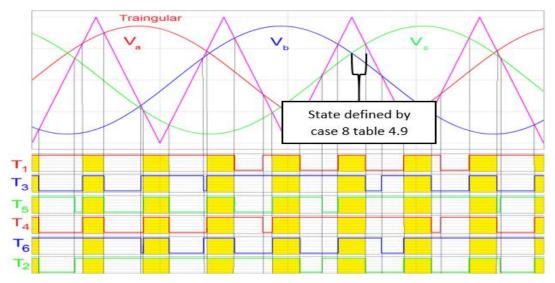

| Figure 3.3: MBC modulating signals showing case 8 in table 4.9 [14]  |    |

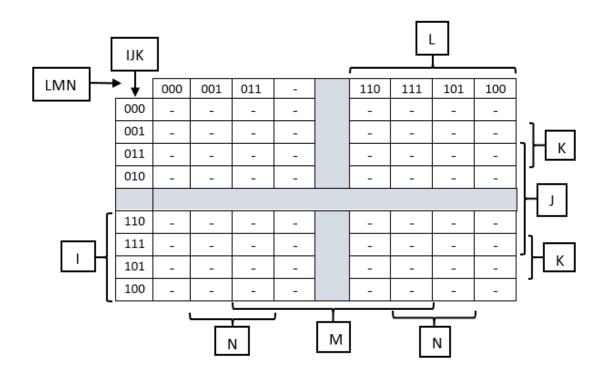

| Figure 3.4: K-map for optimising Boolean equations SSS1 – SSS6       |    |

| Figure 4.1: Basic ZSI block diagram                                  |    |

| Figure 4.2: SPWM technique PWM generator                             |    |

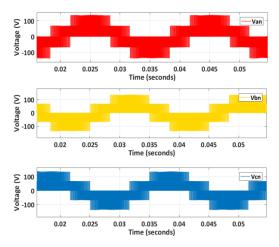

| Figure 4.3: Unfiltered phase voltages (SPWM)                         |    |

| Figure 4.4: Filtered phase voltage (SPWM)                            |    |

| Figure 4.5: Unfiltered line voltages (SPWM)                          |    |

| Figure 4.6: Filtered line voltage (SPWM)                             |    |

|                                                                      |    |

| Figure 4.7: DC-link voltage (SPWM)                                   |    |

|                                                                      |    |

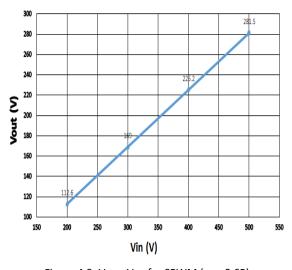

| Figure 4.9: $V_{in}$ vs $V_{out}$ for SPWM (m = 0.65)                |    |

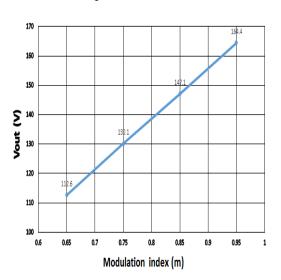

| Figure 4.10: m vs V <sub>out</sub> for SPWM (Vin = 200V)             |    |

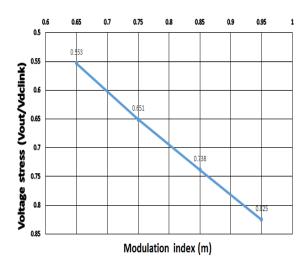

| Figure 4.11: (V <sub>out</sub> /V <sub>dc-link</sub> ) vs m for SPWM |    |

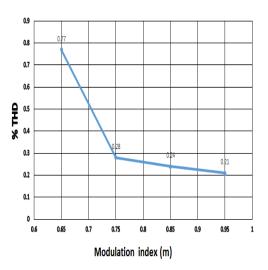

| Figure 4.12: %THD vs m for SPWM                                      |    |

| Figure 4.13: Simple boost technique PWM generator                    |    |

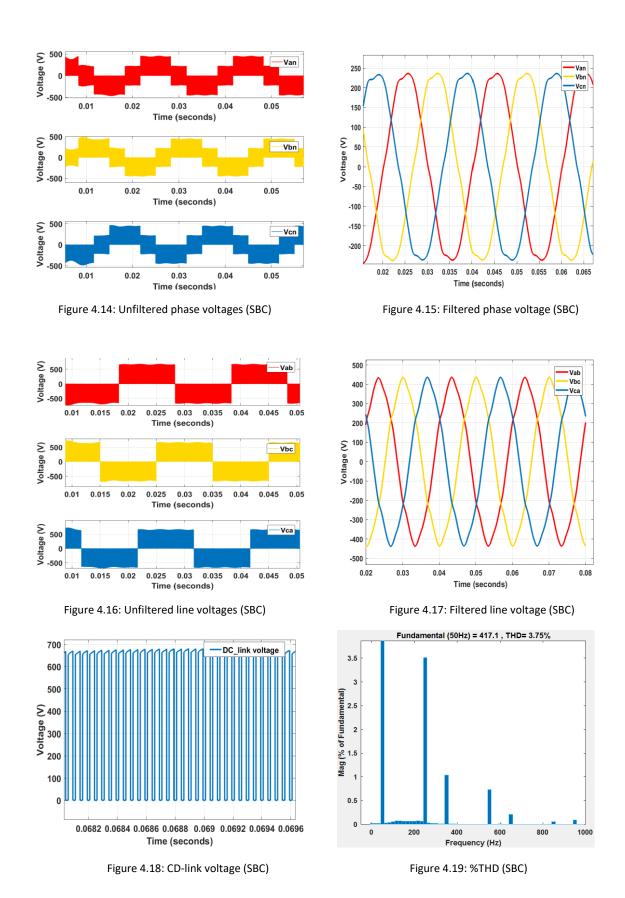

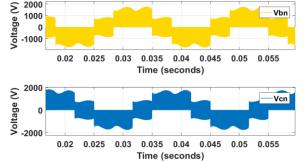

| Figure 4.14: Unfiltered phase voltages (SBC)                         |    |

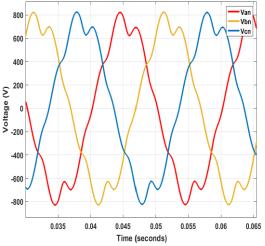

| Figure 4.15: Filtered phase voltage (SBC)                            |    |

| Figure 4.16: Unfiltered line voltages (SBC)                          |    |

| Figure 4.17: Filtered line voltage (SBC)                             |    |

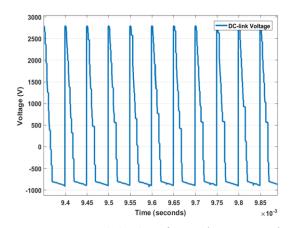

| Figure 4.18: CD-link voltage (SBC)                                   |    |

| Figure 4.19: %THD (SBC)                                              |    |

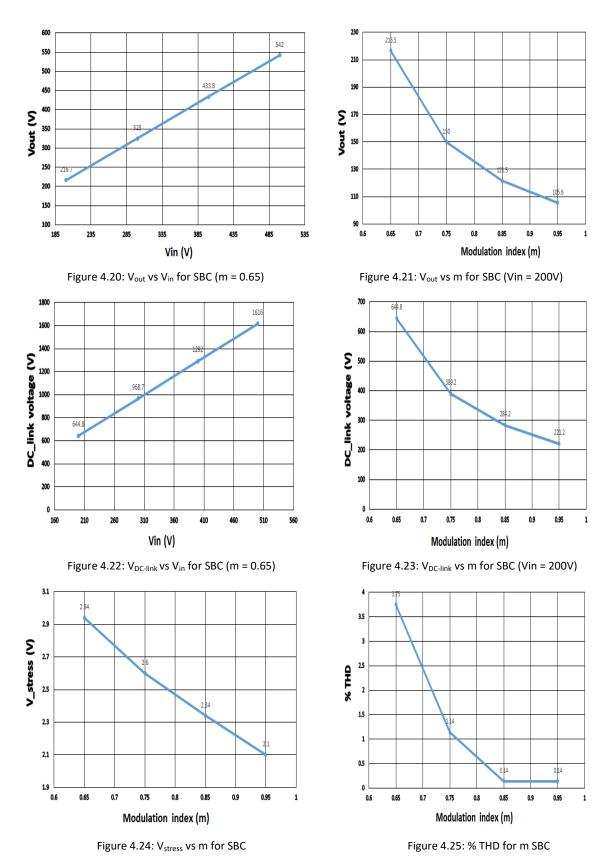

| Figure 4.20: $V_{out}$ vs $V_{in}$ for SBC (m = 0.65)                |    |

| Figure 4.21: $V_{out}$ vs m for SBC (Vin = 200V)                     |    |

| Figure 4.22: $V_{DC-link}$ vs $V_{in}$ for SBC (m = 0.65)            |    |

| Figure 4.23: $V_{DC-link}$ vs m for SBC (Vin = 200V)                 |    |

| Figure 4.24: V <sub>stress</sub> vs m for SBC                        |    |

| Figure 4.25: % THD for m SBC                                         | 48 |

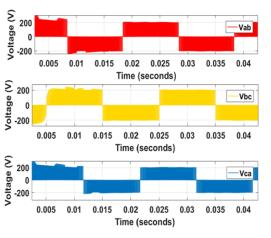

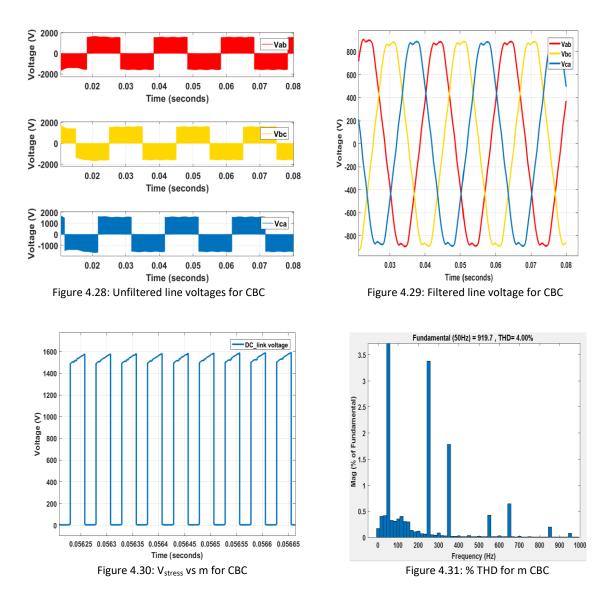

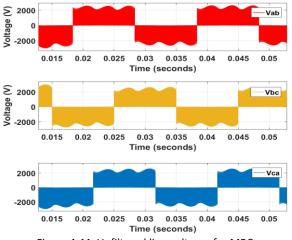

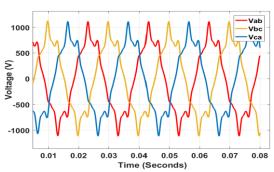

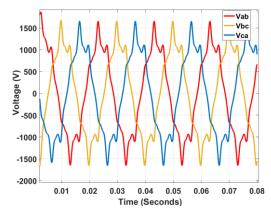

| Figure 4.26: Unfiltered phase voltages for CBC                          | 50  |

|-------------------------------------------------------------------------|-----|

| Figure 4.27: Filtered phase voltage for CBC                             | 50  |

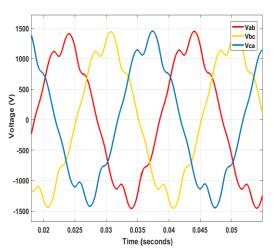

| Figure 4.28: Unfiltered line voltages for CBC                           | 51  |

| Figure 4.29: Filtered line voltage for CBC                              | 51  |

| Figure 4.30: V <sub>stress</sub> vs m for CBC                           | 51  |

| Figure 4.31: % THD for m CBC                                            | 51  |

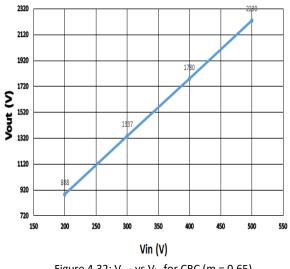

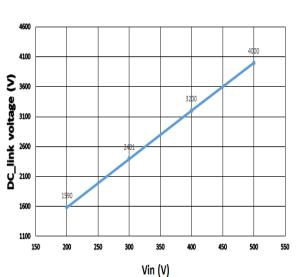

| Figure 4.32: $V_{out}$ vs $V_{in}$ for CBC (m = 0.65)                   | 53  |

| Figure 4.33: V <sub>out</sub> vs m for CBC (Vin = 200V)                 |     |

| Figure 4.34: $V_{DC-link}$ vs $V_{in}$ for CBC (m = 0.65)               | 53  |

| Figure 4.35: V <sub>DC-link</sub> vs m for CBC (Vin = 200V)             |     |

| Figure 4.36: V <sub>stress</sub> vs m for CBC                           | 53  |

| Figure 4.37: % THD for m CBC                                            | 53  |

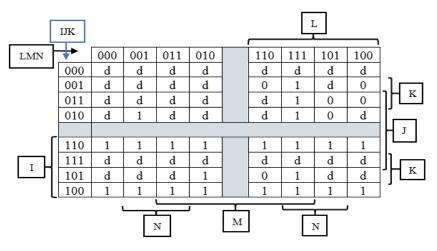

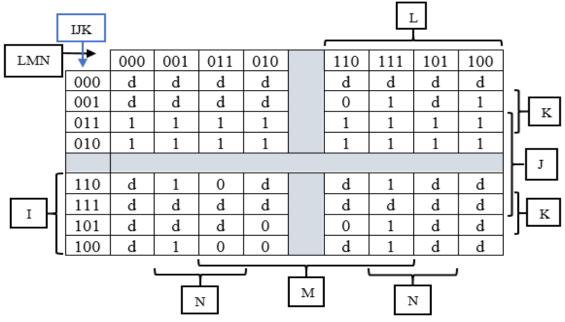

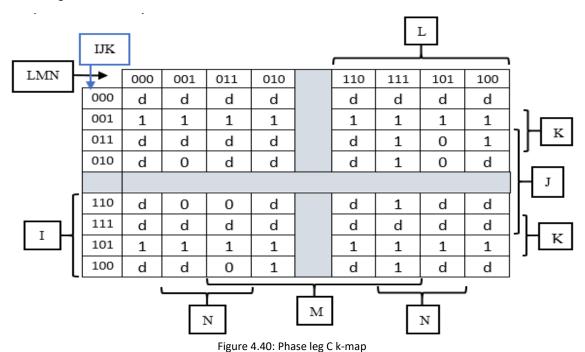

| Figure 4.38: Phase leg A k-map                                          |     |

| Figure 4.39: Phase leg B k-map                                          |     |

| Figure 4.40: Phase leg C k-map                                          |     |

| Figure 4.41: MBC technique PWM generator                                |     |

| Figure 4.42: Unfiltered phase voltages for MBC                          |     |

| Figure 4.43: Filtered phase voltage for MBC                             | 60  |

| Figure 4.44: Unfiltered line voltages for MBC                           |     |

| Figure 4.45: Filtered line voltage for MBC                              |     |

| Figure 4.46: V <sub>stress</sub> vs m for MBC                           |     |

| Figure 4.47: % THD for m MBC                                            |     |

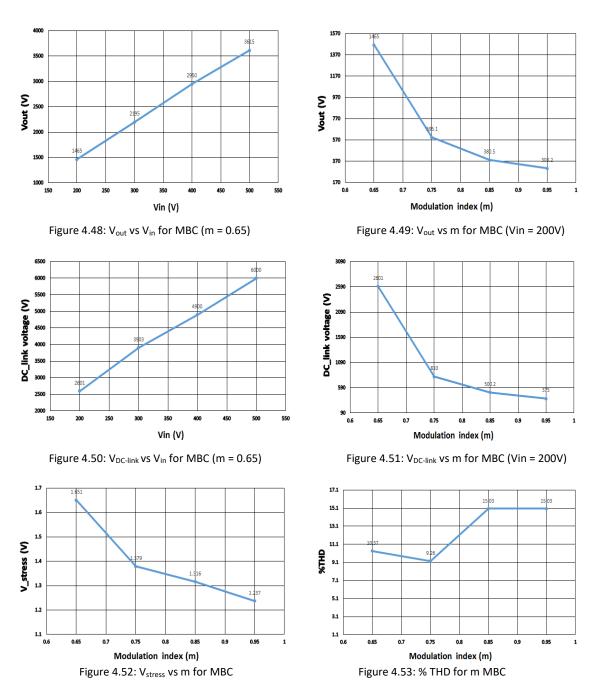

| Figure 4.48: $V_{out}$ vs $V_{in}$ for MBC (m = 0.65)                   |     |

| Figure 4.49: V <sub>out</sub> vs m for MBC (Vin = 200V)                 |     |

| Figure 4.50: $V_{DC-link}$ vs $V_{in}$ for MBC (m = 0.65)               |     |

| Figure 4.51: $V_{DC-link}$ vs m for MBC (Vin = 200V)                    |     |

| Figure 4.52: V <sub>stress</sub> vs m for MBC                           |     |

| Figure 4.53: % THD for m MBC                                            |     |

| Figure 5.1: Boost factor vs modulation index (SBC, CBC and MBC)         |     |

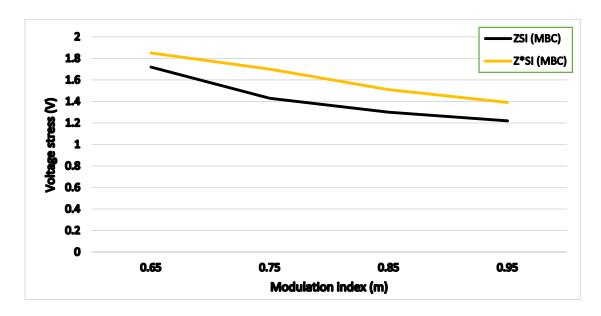

| Figure 5.2: Voltage stress vs modulation index (SBC, CBC and MBC)       |     |

| Figure 5.3: The proposed CB-ZSI topology                                |     |

| Figure 5.4: Equivalent shoot-through circuit CB-ZSI                     |     |

| Figure 5.5: Equivalent non-shoot-through CB-ZSI                         |     |

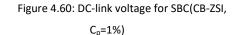

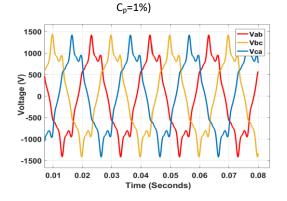

| Figure 5.6: Filtered phase voltage for SBC(CB- ZSI,C <sub>p</sub> =1%)  |     |

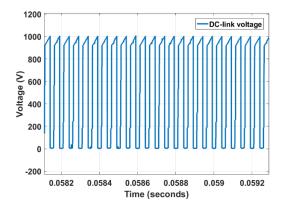

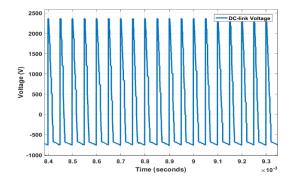

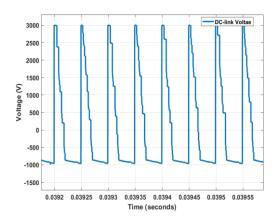

| Figure 5.7: DC-link voltage for SBC(CB-ZSI, $C_p=1\%$ )                 |     |

| Figure 5.8: Filtered phase voltage for SBC (, C <sub>p</sub> =2%)       |     |

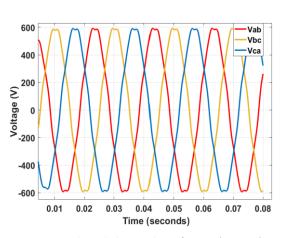

| Figure 5.9: DC-link voltage for SBC (CB-ZSI, $C_p$ =2%)                 |     |

| Figure 5.10: Filtered phase voltage for CBC(CB-ZSI, $C_p=1\%$ )         |     |

| Figure 5.11: DC-link voltage for CBC(CB-ZSI, C <sub>p</sub> =1%)        |     |

| Figure 5.12: Filtered phase voltage for CBC(CB-ZSI, C <sub>p</sub> =1%) |     |

| Figure 5.13: DC-link voltage for CBC(CB-ZSI, C <sub>p</sub> =2%)        |     |

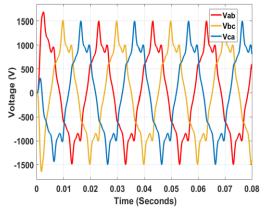

| Figure 5.14: Filtered phase voltage for MBC(CB-ZSI, C <sub>p</sub> =1%) |     |

| Figure 5.15: DC-link voltage for MBC(CB-ZSI, C <sub>p</sub> =1%)        |     |

| Figure 5.16: Filtered phase voltage for MBC(CB-ZSI, C <sub>p</sub> =2%) |     |

| Figure 5.17: DC-link voltage for MBC(CB-ZSI, C <sub>p</sub> =2%)        |     |

| Figure 5.18: Boost factor vs modulation index (ZSI vs CB-ZSI at SBC)    |     |

| Figure 5.19: Boost factor vs modulation index (ZSI vs CB-ZSI at CBC)    |     |

| Figure 5.20: Boost factor vs modulation index (ZSI vs CB-ZSI at CBC)    |     |

| Figure 5.21: Voltage stress vs modulation index (ZSI vs CB-ZSI at MBC)  |     |

| Figure 5.21: Voltage stress vs modulation index (ZSI vs CB-ZSI at SBC)  |     |

| Figure 5.23: Voltage stress vs modulation index (ZSI vs CB-ZSI at CBC)  |     |

| i iguio 3.23. Toimgo buobb to modulation mach (201 to CD-201 at MDC)    | , , |

# LIST OF TABLES

| Table 3.1 Sample table for collecting results                      | 30 |

|--------------------------------------------------------------------|----|

| Table 4.1: Truth table for the traditional ZSI mode PWM controller | 37 |

| Table 4.2: Summary of VSI mode results                             | 40 |

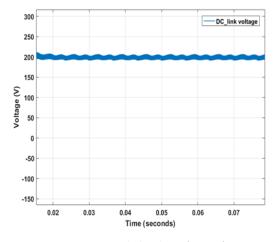

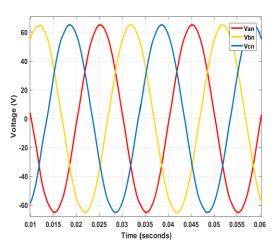

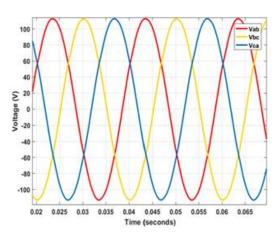

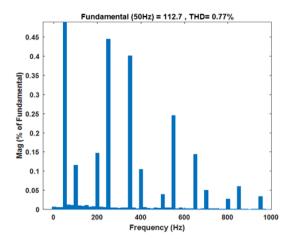

| Table 4.3: Summary of figure 4.7 and 4.8 results                   | 43 |

| Table 4.4: Truth table for the simple boost PWM controller         | 44 |

| Table 4.5: Summary of SBC mode results                             | 47 |

| Table 4.6: Theoretical vs practical parameters for SBC method      |    |

| Table 4.7: Summary of CBC mode results                             | 52 |

| Table 4.8: Theoretical vs practical parameters                     | 54 |

| Table 4.9: Truth table for the maximum boost PWM controller        | 56 |

| Table 4.10: Summary of MBC mode results                            | 61 |

| Table 4.11: Theoretical vs practical parameters                    | 63 |

| Table 5.1: Summary of SBC mode results (CB-ZSI)                    | 72 |

| Table 5.2: Summary of CBC mode results (CB-ZSI)                    | 73 |

| Table 5.3: Summary of MBC mode results (CB-ZSI)                    | 73 |

| Table 5.4: ZSI vs CB-ZSI ( $C_p = 1$ and 2%) at SBC, CBC and MBC   | 74 |

# LIST OF ABBREVIATIONS

VSI Voltage-Source Inverter

CSI Current-Source Inverter

ZSI Z-Source Inverter

CB-ZSI Capacitor Boosted-Z-Source Inverter

PWM Pulse Width Modulation

SBC Simple Boost Control

CBC Control Boost Control

MBC Maximum Boost Control

SPWM Sine Pulse Width Modulation

UPS Uninterruptible Power Supply

DVR Dynamic Voltage Restorer

PV Photo-Voltaic

VSD Variable Speed Drive

MPPT Maximum Power Point Tracking

EMI Electro-Magnetic Interference

K-map Kanaurgh-Map

POS Product Of Sums

SOP Sum Of Products

SANS South African National Standards

IGBT Insulated Gate Bipolar Transistor

MOSFET Metal-Oxide Semiconductor Field-Effect Transistor

#### 1. INTRODUCTION

#### 1.1. Introduction of the research work undertaken

This research study investigates a DC-AC converter called a Z-source inverter (ZSI). A ZSI is a novel topology of a DC-AC converter that was proposed in 2002 by Professor F.Z. Peng and has proven to overcome most of the performance issues faced with the traditional topologies which are the voltage-source inverters (VSI) and current-source inverters (CSI). This has led to ZSIs and ZSI related projects appearing more frequently in literature and finding applications in industries [1], [2], [3].

Therefore, this particular study focuses on the capability of ZSI at different operating input conditions and different PWM control techniques and hence proposes a different topology of an inverter aimed to improve performance capacity relative to that of a classical inverter.

#### 1.2. Motivation

ZSIs have numerous renewable energy and industrial applications. Renewable energy applications include photo-voltaic (PV) power and wind power while industrial applications include uninterruptible power supplies (UPS), voltage sag mitigation (DVR), etc.

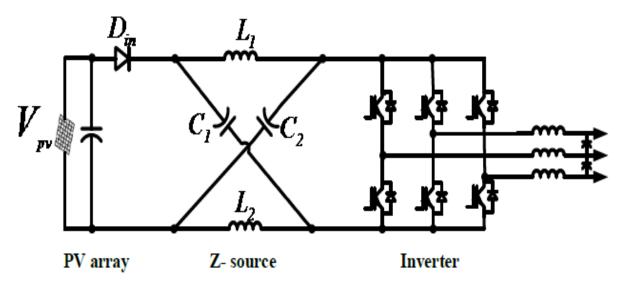

Solar power or more specifically photovoltaic power is one of the most promising sources of electrical power for the future. This is due to the capability of distributed PV (photovoltaic) generators to be synchronized to the national utility grid. Apart from augmenting the capacity of distribution systems, PV systems have various other benefits such as deferring capital investments on distribution and transmission systems, improving power quality and improving system reliability [4], [5]. A maximum power point tracking algorithm (MPPT) has been proposed to maximize the yield of PV power systems which is also one of the reasons behind PV grid-tie systems' success [5]. Figure 1.1 below shows a photovoltaic cell connected to a ZSI for the above-stated application.

Figure 1.1: PV-cell connected to a ZSI [4]

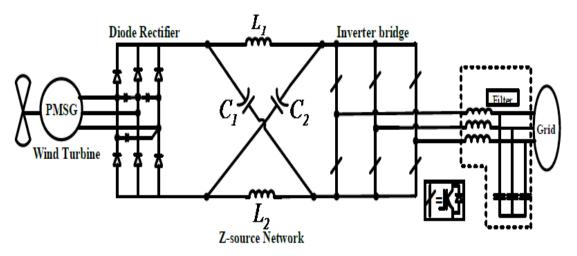

It is approximated that 100 Giga-Watts can be harvested from off-shore winds across the globe [6]. However; off-shore wind farms are usually far away from areas where power is required which calls for lengthy transmission systems. These transmission systems are associated with transmission losses and transmission voltage drops and hence high gain transformers are normally required part of a transmission system thus implying more costs to transmission systems. Incorporation of a ZSI in a transmission system renders a high gain transformer redundant because a ZSI can boost up to infinity (theoretically) and when used with a properly designed filter they eliminate a large amount of harmonics distortion [2], [6]. Figure 1.2 below shows a wind turbine connected to a ZSI through a full bridge rectifier for the above-stated application.

Figure 1.2: Wind turbine connected to a ZSI [6]

Uninterruptible power supplies are devices that provide power to critical loads when the main power fails. Transformers or DC-DC convertors (boost converters) can be used to step-up the voltage in a UPS, however; using a ZSI for this purpose results in much better performance of a UPS. ZSIs give UPSs a capacity of higher peak-to-peak output voltage as compared to when a

transformer or a boost converter is used for the same purpose. ZSIs together with filters reduce the percentage of total harmonics distortion caused by linear or unbalanced loads connected to a UPS [7]. Figure 1.3 below shows a circuit diagram of a ZSI based UPS system.

Figure 1.3: ZSI based UPS system [7]

It is approximated that 92% of electrical power systems disturbances is due to voltage sags [8]. Therefore, voltage sags incur serious economic losses to industry and as a result, sensitive equipment should be protected against them. Voltage sag is a sudden reduction in amplitude of a voltage signal by between 0.1 to 0.9 pu (per unit) [8], [9]. Voltage sags are usually mitigated via dynamic voltage restorers (DVR). These devices inject an appropriate amount of voltage, depending on the amount of sag, in series with the supply terminals to compensate for the voltage drop it sees.

Classical DVRs contain voltage source (VSI) inverters however with voltage limitations since VSIs have output voltages of equal or less than its input voltage. Nowadays DVRs are increasingly being based on ZSIs since they overcome most issues (boost factor, reliability, %THD, ETC) faced with VSIs based DVRs [8], [9]. Figure 1.4 below shows a ZSI base DVR connected in series between a source and a load.

Figure 1.4: ZSI based DVR system [9]

Other applications of ZSIs include variable speed drives (VSD), vehicular drives, grid-tie systems, etc. Literature shows that there are numerous uses of ZSIs which render the study of this dissertation relevant since ZSIs are a focus of researchers and have a significant role in the recent technology of convertors.

# 1.3. Research question

The problem statement for this research study is to investigate the performance impact of different pulse width modulation (PWM) techniques on a three-phase Z-source inverter. The knowledge gain from the aforementioned study is used to propose a different inverter topology whose performance should show improvement from that of a classical Z-source inverter.

#### 1.4. Background

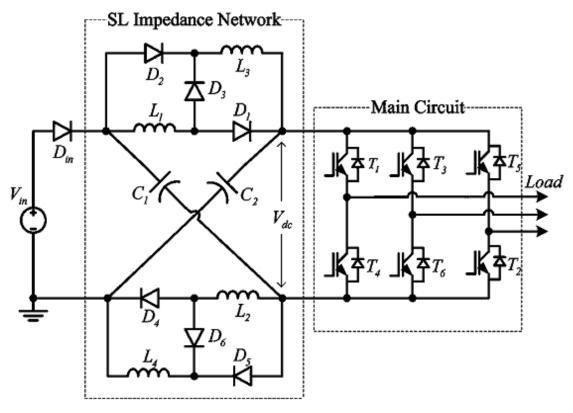

From the date when ZSIs were proposed, a substantial amount of have been published under the name of these inverters [10], [11]. Miao Zhu et al. proposed a switched inductor Z-source inverter (SL-SZI). Figure 1.5 below shows a circuit diagram of an SL-ZSI. This inverter has a DC-power source in series with an input diode  $D_{in}$ , an SL-impedance network and a three-phase universal bridge. An SL-impedance network is a distinction of an SL-ZSI from a ZSI. SL-impedance network has two additional inductors  $L_3$  and  $L_4$  as well as 6 diodes  $D_1$  to  $D_6$  on top of two capacitors and two inductors ( $L_1$ ,  $L_2$  and  $C_1$ ,  $C_2$ ) that a traditional Z-impedance network has.

Figure 1.5: A switched inductor Z-source inverter [10]

This topology proved to improve voltage adjustability. The voltage boost is greatly improved. This occurs because, for an SL-ZSI, a very short shoot-through time interval T<sub>0</sub> is required to obtain large voltage gain that would otherwise require a much longer shoot-through interval in a classical ZSI. This has a good overall impact on the quality of output waveforms of an SL-ZSI by reducing the percentage of total harmonic distortion (%THD). SL-ZSIs also offer voltage buck ability that needs low AC voltage and the concept of SL-ZSIs can find application in AC-AC, DC-DC, and AC-DC apart from DC-AC converters. PWM control techniques known to literature such as SBC, CBC, MBC, etc. apply to SL-ZSIs [10], [11].

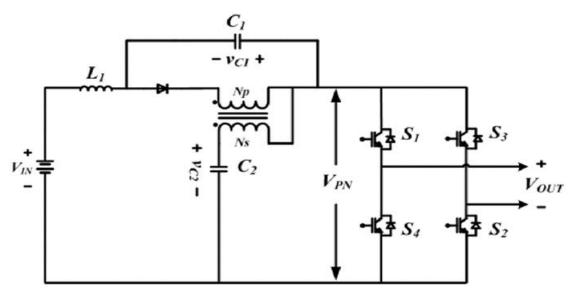

*M. Adamowicz* and S. Diva et al. proposed trans-Z-source inverters. In their work, they proposed an Inductor-Capacitor-Capacitor-Transformer-Z-source inverter (LCCT-ZSI) and an inductor-capacitor-transformer-quazi-Z-source inverter (LCCT-qZSI). Figures 1.6 and 1.7 below show an LCCT-ZSI and an LCCT-qZSI respectively [9].

Figure 1.6: An LCCT-ZSI [13]

Figure 1.7: An LCCT-qZSI [13]

LCCT-ZSI in figure 1.6 holds two capacitors connected on either side of a transformer to prevent the transformer core from blocking DC [9]. LCCT-qZSI in figure 1.7 contains one capacitor connected shunt to a transformer to suppress voltage ripples at the transformer output [12]. Both topologies show significant improvement on the boost and hence the gain factor on the overall inverter, however; an LCCT-ZSI supersedes LCCT-qZSI in the voltage boosting capability because of capacitor C<sub>1</sub> which maintains a residual voltage across the impedance network at steady state [9], [12]. LCCT-qZSI shows great power conversion efficiency over LCCT-ZSI because of the LCCT-qZSI's impedance network ability to store more energy compared to LCCT-

ZSIs. In both LCCT-ZSIs and LCCT-qZSIs; greater voltage gains are possible by decreasing a transformer's turn's ratio [9].

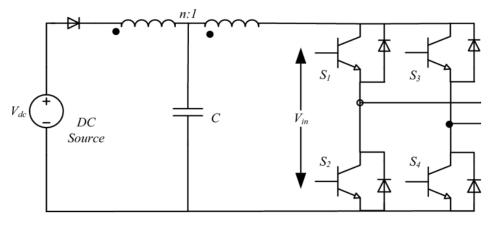

*S.M. Dehghan* et al. proposed topology of Z-source inverter with two dc inputs and two ac outputs, termed a dual-input-dual-output Z-source inverter (DIDO-ZSI) [9]. Figure 1.8 below shows a circuit diagram of DIDO-ZSI.

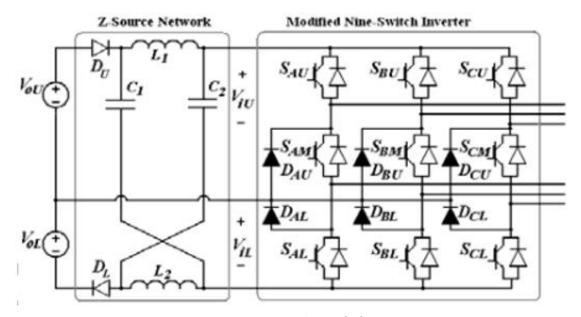

Figure 1.8: A DIDO-ZSI circuit diagram [17]

This inverter has two DC input power sources and two three-phase outputs. An impedance network is similar to that of a classical ZSI except for an additional diode  $D_L$  connected in series to  $L_2$ . The inverting stage is made of nine switching devices hence its name, the nine-switch inverter. Each of these switching devices has an anti-parallel diode or free-wheeling diode. This diode provides a bidirectional current flow and unidirectional voltage blocking capability. A DIDO-ZSI is composed of two upper and lower inverters. Three upper switching devices, three mid-switching devices and three lower diodes ( $D_{AL}$ ,  $D_{BL}$  &  $D_{CL}$ ) form the upper inverter [13], [14].

The output of the upper inverter is connected to the positive terminal of  $V_{iU}$  via upper switching devices and is connected to the negative terminal of  $V_{iU}$  via mid switching devices and lower extra diodes. The lower inverter includes three mid-switching devices, three lower switching devices and three upper extra diodes ( $D_{AU}$ ,  $D_{BU}$  &  $D_{CU}$ ). The output of the inverter is connected to the positive terminal of  $V_{iL}$  via mid-switches and upper diodes and connected to the negative terminal of  $V_{iL}$  via lower switches [9], [13], [14].

This inverter can boost a DC voltage to any required level and can control amplitude, frequency, and phase independently [13]. DIDO-ZSI can be used in applications that require two unregulated

DC-power sources feeding two independent loads. Both AC outputs remain operational even if one DC-power source is lost. This topology requires much less passive components rating as compared to those that would have been required in two independent ZSIs of the same capacity as one DIDO-ZSI [13].

Apart from the above-mentioned pieces of work, a lot more has been done under the name of Z-source inverters. *A. Pattanaphol et al.* used Z-source inverter to study the shading issue of photovoltaic cells [9]. Po Xu et al. introduced Z-source inverter for grid associated photovoltaic systems termed solar-powered grid-tie Z-source inverters [5]. *Omar Ellabban et al.* proposed a technique to control the speed of the motor using a bidirectional Z-source inverter [15] . *R. Senthikumar et al.* proposed a Z-source inverter for uninterruptible power supply (UPS) applications [16].

Therefore, when looking at the time when Z-source inverters were first introduced (2002) against the amount of work that researchers have done since then, one can conclude that Z-source inverters have taken attention of many researchers and that they are one successful family of power convertor that has found many different applications in our modern world.

## 1.5. Thesis aims and objective

The purpose of this research is to study the behaviour of a ZSI in response to different PWM control techniques or rather; the effect of different PWM techniques on a ZSI over a range of operating conditions. Furthermore; the knowledge gained from the latter mentioned study is then to be carefully utilized to develop an amendment to a classical ZSI to improve its response to the PWM control techniques, hence improving the power quality of a ZSI. Therefore; this study broadly separates a design of a ZSI into two main tasks, viz. the design of the main ZSI circuit as well as the design of a PWM control technique modulation a ZSI to output a desired waveform.

A ZSI is designed after which three most common PWM control techniques in literature [5], [17], [18]; viz. simple boost control (SBC), constant boost control (CBC), as well as maximum boost control (MBC), are formulated. These PWM control techniques are then applied to a ZSI and the operating conditions such as an input voltage ( $V_{in}$ ) and modulation index (m) are varied while paying close attending to the key performance parameters of a ZSI. The key performance parameters include DC-link voltage ( $V_{DC-link}$ ), boost factor (B), Gain factor (G), Output voltage amplitude ( $V_{ac}$ ), Voltage stress across switching devices ( $V_{stress}$ ) as well as the percentage of total harmonic distortion (%THD).

The relationships between the input and/or performance parameters are studied and understood. The gained knowledge is hence used to propose a different topology called Capacitor Boosted-

Z-Source Inverter (CB-ZSI). The naming of this topology is motivated by the fact that an amendment was done on a Z-impedance network of a classical ZSI in to transform it into a CB-Z-impedance network.

This proposed topology aims to improve the performance of an inverter and hence its output power quality by improving the key performance parameters (boost factor, gain factor, voltage stress across switching devices, etc.) in response to a range of input variables (input voltage, modulation index) at different PWM control techniques. The key performance parameters of a ZSI should serve as the asymptotes (baseline) for those of a CB-ZSI; that is, CB-ZSI's key performance parameter should always be better than those of a ZSI.

## 1.6. Thesis organization

Chapter 2 explains the theoretical background on three-phase Z-source inverters, three-phase low-pass filters and different PWM control techniques for three-phase Z-source inverters. The merits of ZSIs over voltage-source and current-source inverters are stated and the operation of ZSIs is explained in detail hence formulating the inverters' output equation. LC and LCL filter advantages and disadvantages are discussed based on their appropriateness to ZSI's power quality improvement. Lastly, simple boost, constant boost and maximum boost PWM control techniques are discussed stating distinctions amongst each other.

Chapter 3 discusses the methodology of this paper. The sequence of design and techniques used in the design of the simulation is explained. The method of collecting data from the simulated prototype is also explained which includes a specific design of data collection tables and the selection of ranges in which data is collected. Lastly, the criteria for judging improved or worse performance for the proposed CB-ZSI in chapter 5 is explained.

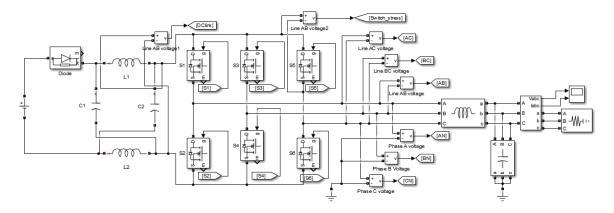

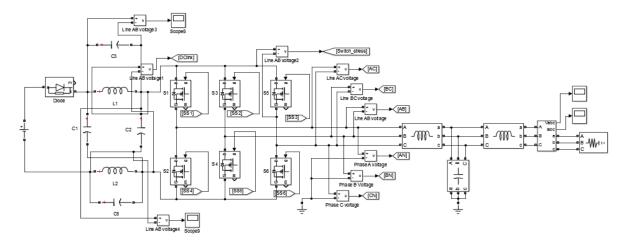

Chapter 4 implement what has been discovered in the literature in chapter 2. A classical ZSI is designed and implemented in MATLAB/SIMULINK. Simple boost, constant boost and maximum boost are also designed and applied to a ZSI. Input parameters are varied while collecting data for each PWM control technique using a specially designed table in chapter 3 to collect enough data. The collected data is then analysed and the conclusion is made on the performance of a ZSI at these different PWM control techniques.

Chapter 5 proposes a new topology, called a CB-ZSI, whose aim is to improve the performance from that of a classical topology investigated in chapter 4. Simple boost, constant boost and maximum boost PWM control techniques are applied to this topology while collecting the same data that was collected for a classical ZSI in chapter 4. This data is analysed and results are compared to baseline results that were obtained in chapter 4. A conclusion is then made on

whether a CB-ZSI has improved or worse performance relative to a classical ZSI based on criteria stated in chapter 3.

Chapter 6 gives an overall conclusion of this paper. In this chapter, it is stated whether the main aim and objectives stated in chapter 1 were fulfilled or not. If not; what more actions could have been done to fulfil them? Chapter 6 also features a summary of future directions to build on top work presented by this research study.

#### 2. LITERATURE REVIEW

A Z-source inverter is a recent topology of inverter that was proposed in 2002 by Professor *F. Z. Peng* [6], [8], [9]. Before its proposition, a voltage-source and a current-source inverter, abbreviated as VSI and CSI respectively, were the common topologies used for inverting related applications such as interfacing the PV power to the utility grid [6], [7], [9], [13].

# 2.1. A voltage-source inverter (VSI)

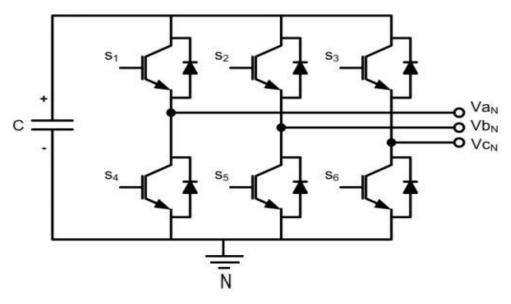

Figure 2.1: A traditional VSI [8]

Figure 2.1 shows a basic circuit of a traditional three-phase voltage-source inverter. A DC power source in parallel with a relatively large capacitor forms a DC voltage source that feeds the main inverting stage. Depending on the application of a VSI; a DC power source can be a battery, fuel cell stack, diode rectifier, and/or capacitor [8]. In a PV system application, a DC power source is a PV cell or an array of PV cells [3], [6]. A bridge comprises six electrical controlled switching devices (IGBTs/MOSFETs) each comprising of a power transistor and an anti-parallel or free-wheeling diode. This diode provides a bidirectional current flow and unidirectional voltage blocking capability. Despite VSIs' popularity in converting applications, it has conceptual and theoretical barriers and limitations [3], [6], [7], [9], [13].

The output voltage of a VSI is either limited to voltages ranging below or above the DC-link voltage. That is, the VSI either boosts or bucks the input voltage. When operating in the inverter mode (DC-AC power flow) the VSI bucks the input voltage and boost it in the rectifier mode (ACDC power flow). For applications where overdrive is desirable and the available dc voltage is limited, an additional dc-dc boost converter stage is needed to obtain the desired ac output.

This additional stage increases the overall costs of the system and compromises the overall system's efficiency [6], [7], [9].

The upper and lower switching devices of the same phase leg cannot be simultaneously gated-on as this would cause a shoot-through condition (single-phase leg, any two-phase legs or all three-phase legs shorted) consequently destroying a VSI. In some cases, electromagnetic Interference (EMI) noise mistakenly gate-on switching devices resulting in a shoot-through condition and that is a major drawback to VSI's reliability. In response to this issue with VSIs, engineers have adopted 'dead time' to block upper and lower switching devices from switching-on simultaneously thus preventing a shoot-through condition from occurring. However; 'dead-legs' results in more waveform distortion, etc. thus compromising the quality of the output power [3], [6], [7], [9], [12], [13].

## 2.2. A current-source inverter (CSI)

Figure 2.2: A traditional CSI [19]

IGBT switch

Figure 2.2 shows a basic circuit of a traditional three-phase current-source inverter. A DC source is formed by connecting a DC power source in series with a relatively large inductor. The switching devices (IGBTs/MOSFETs) are traditionally composed of power switching devices with reverse block capability such as a gate-turn-off thyristor (GTO), silicon controlled switches (SCR) or power transistors with series diodes. These series diodes provide unidirectional current

flow and bidirectional voltage blocking capability. A CSI also has conceptual and theoretical barriers and limitations [1], [11], [17], [19].

Similar to the VSIs, the output voltage of the CSI is either limited to voltages ranging below (bucks) or above (boosts) the DC-link voltage. When operating in the inverter mode (DC-AC power flow) the CSI bucks the input voltage and boosts it operating in the rectifier mode (AC-DC power flow). For applications where overdrive is desirable and the available dc voltage is limited, an additional dc-dc boost converter stage is needed to obtain the desired ac output. This additional stage increases the overall costs of the system and compromises the system's efficiency [12], [17].

At least one upper switching device and one of the lower switching devices should be gated on and maintained so at any time. Else, the open circuit of a DC inductor would occur consequently destroying the inverter. In some cases, Electromagnetic Interference (EMI) noise mistakenly gate-off the switching devices resulting in the open circuit of the DC inductor and that is a major drawback to CSI's reliability. In response to this issue with CSIs, engineers have adopted 'overlap time' for safe current commutation to prevent this open circuit of a DC inductor condition from occurring. However; 'overlap time' results in more waveform distortion, etc. thus compromising the quality of the output power [7], [9], [12].

The main switching devices of a current source inverter have to block reverse voltage; that requires a series diode to be used in combination with high-speed and high-performance transistors such as insulated gate bipolar transistors (IGBT). This prevents the direct use of low-cost and high-performance IGBT modules and intelligent power modules (IPMs) [10], [17], [19].

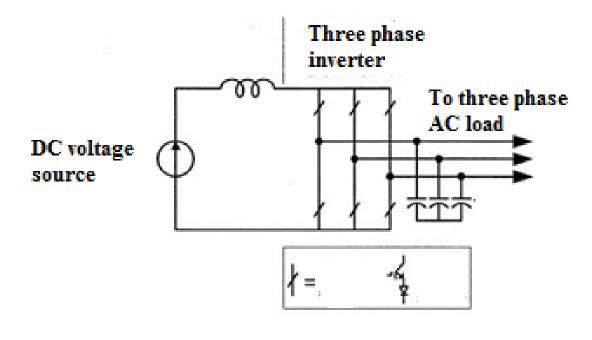

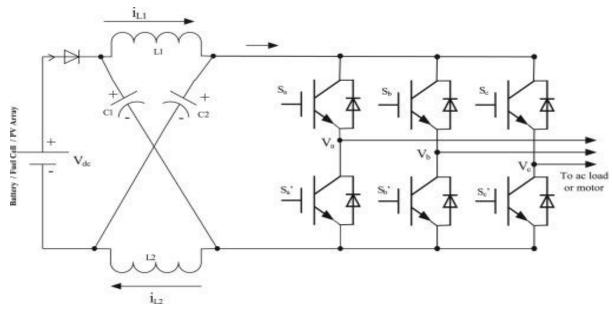

On top of the above-mentioned issues with regards to VSIs and CSIs, both these inverter topologies also suffer some common drawbacks. VSIs and CSIs either buck or boost the input voltage, they cannot buck-boost. This implies that the obtainable output voltage is limited to voltages either greater or below the input voltage [1]. The main circuitries of VSIs and CSIs are not interchangeable. The main circuit of the VSI cannot be used for the CSI application and the opposite is also true [1], [10], [19]. Both VSIs and CSIs are vulnerable to EMI noise which compromises their reliability. Z-source inverters have proven to overcome most of the VSIs' and CSIs' drawbacks. This is the motive behind the focus of researchers on the Z-source inverters. Figure 2.3 shows a basic diagram of a ZSI which has a DC input (battery/fuel cell/PV array), a Z-impedance network (L<sub>1</sub>, L<sub>2</sub> and C<sub>1</sub>, C<sub>2</sub>) and a three-phase universal bridge made of switching devices (S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, S<sub>4</sub>, S<sub>5</sub> and S<sub>6</sub>).

Figure 2.3: The basic ZSI circuit [6]

#### 2.3. A classical three-phase Z-source inverter topology

#### 2.3.1. A general overview

A z-source inverter is an improvement from the two above mentioned inverter topologies, viz. the VSI and CSI. As mentioned earlier, the ZSI overcome most of the conceptual and theoretical barriers and limitations that come with both the VSIs and CSIs. With a z-source inverter, an output ac voltage can theoretically be any value ranging from zero to infinity regardless of the input voltage [7], [9]. This implies that a z-source inverter is a buck-boost converter with a wide range of possible output voltages. Unlike traditional VSIs and CSIs which possess eight switching states or vectors, ZSIs have a ninth switching state called the shoot-through state which gives it the boosting capability. This shoot-through state is similar to the one mentioned earlier which is responsible for severe damage and unreliability in the case of VSIs. Therefore, a ZSI takes advantage of a VSI's weakness and makes it its strength instead.

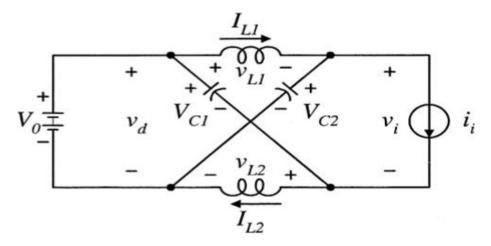

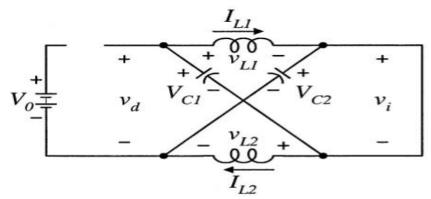

Depending on the switching state, the operation of a ZSI can be classified into three modes of operation. The first mode occurs during one of the six active states. Active states occur when a DC-input voltage appears across the inductor and a capacitor ( $C_1$  and  $L_2$  or  $C_2$  and  $L_1$ ). During this mode, capacitors  $C_1$  and  $C_2$  are charged and stay charged at steady-state and energy flow to the load via the inductor. An inverter bridge can be seen as a current source when looking from the DC-link voltage [7], [9], [12].

The second mode occurs when a ZSI is operating in one of the two zero states. Zero states occur when the bridge short circuits the load either by all three upper or lower switching devices [3]. A

DC-input voltage appears across the inductor and a capacitor ( $C_1$  and  $L_2$  or  $C_2$  and  $L_1$ ) except that no current flow through them. A bridge can be taken as an open circuit in this mode [17], [19].

The third mode occurs when a ZSI is operating in one of the seven shoot-through states. Shoot-through can occur when any single-phase legs are shorted (3 possibilities; A or B or C), any two phase legs shorted (3 possibilities; AB or BC or AC) and when all three phases are shorted (1 possibility; ABC) [9], [17]. During this mode, a bridge can be seen as a short circuit when looking from the DC-link voltage and there is no voltage across the load. The capacitor voltage is boosted to the required value depending on the amount of shoot-through time (T<sub>0</sub>). T<sub>0</sub> is inserted on portions of zero states or whole zero states (Depending on the PWM control technique used to give a ZSI the necessary boosting capabilities [3], [6], [7], [9]. Figures 2.4 and 2.5 show equivalent circuits of a ZSI when operating in non-shoot-through (mode 1 and mode 2) and shoot-through (mode 3) mode.

Figure 2.4: The ZSI in non-shoot-through state (mode 1 and 2) [3]

Figure 2.5: The ZSI in the shoot-through state (mode 3) [3]

When the ZSI is in the non-shoot-through state the inverter bridge is represented by a current source as seen from Figure 2.4. It is important to note the following; during any of the six active states, an inverter bridge is represented by a current source with finite current while during any of the two zero states, an inverter bridge is represented by a current source with zero current (open

circuit) [17]. When a ZSI is in shoot-through state the inverter bridge is represented by a short circuit as seen in Figure 2.5.

#### 2.3.2. The circuit analysis

The analysis of a ZSI assumes that a z-impedance is symmetrical. That is;  $C_1$  is equal to  $C_2$  and  $L_1$  is equal to  $L_2$ . This assumption results to (2.1) below:

$$V_{C1} = V_{C2} = V_{C_1} V_{L1} = V_{L2} = V_{L}$$

2.1

During a shoot-through state ( $T_0$  interval):

$$V_L = V_C, V_{DC-link} = 0$$

During a non-shoot-through state ( $T_1$  interval):

$$V_L \neq V_C$$

$$V_L = V_{in} - V_C = V_C - V_{DC-link}$$

$$\therefore \widehat{V_{DC-link}} = V_C - V_L = 2V_C - V_{in}$$

2.3

It should be noted that  $V_{in}$  and  $V_{DC\text{-link}}$  refer to  $V_0$  and  $V_i$  respectively in figures 2.4 and 2.5. The average inductor voltage across inductors  $L_1$  and  $L_2$  is zero at steady state. This can be deduced from a definition of an inductor voltage which states that it is equal to a product of an inductor's characteristic inductance and a differential of current through it [3], [6], [7], [9], [12], [13]. [20] Average inductor voltage-time product  $(T = T_1 + T_0 \text{ interval})$ :

$$\overline{V_L} \times T = V_C \times T_0 + (V_{in} - V_C) \times T_1 = 0$$

$$\therefore \frac{V_C}{V_{in}} = \frac{T_1}{T_1 - T_0}$$

Average and peak DC-link voltage-time product ( $T = T_1 + T_0$  interval):

$$\overline{V_{DC-link}} \times T = V_C \times T$$

, at steady state

$$\therefore \widehat{V_{DC-link}} = 2V_C - V_{in}$$

$$\widehat{V_{DC-link}} = \frac{T_1}{T_1 - T_0} \times V_{in} - V_{in}$$

(2.4 substituted in to 2.3)

$$\widehat{V_{DC-link}} = \frac{2T_1 - T_1 + T_0}{T_1 - T_0} \times V_{in}$$

$$\therefore \frac{\widehat{V_{DC-link}}}{V_{in}} = \frac{T_1 + T_0}{T_1 - T_0}$$

$$\frac{\widehat{V_{DC-link}}}{V_{in}} = \frac{T_1 + T_0}{T_1 + T_0 - 2T_0} \text{ (substitute T} = T_1 + T_0)$$

## 2.4. The output filter design

Generally; harmonics in DC-AC converters can be removed by inserting an appropriate filter of high inductance [20], [21]. Inductive filters are easy to design but in the practical application of several kilowatts, inductive filters become expensive due to the large size of inductor and the dynamic response of the system becomes poor [20]. In the case of the ZSI application, the low pass filter is the one required to filter the high-frequency harmonics and pass-on low-frequency components. The most common low-pass filters are the LC and the LCL filters [22].

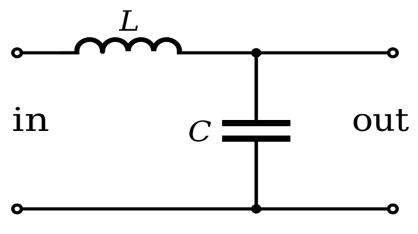

#### 2.4.1. LC-filter

Figure 2.6 shows a typical circuit diagram of an LC-filter which has a series inductor (L) and a shunt capacitor(C) with  $V_{in}$  being the inverter side while  $V_{out}$  is the load side. It should be noted that for three-phase systems, figure 2.6 is considered as a per-phase equivalent representation of a three-phase LC filter.

Figure 2.6: An LC filter [22]

LC-filters consist of a parallel capacitor and a series inductor. The addition of a parallel capacitor is an improvement from L-filter. This amendment of an L-filter to an LC-filter decreases a required inductance for the latter, thus reducing the overall cost and operational losses of LC-filter compared to L-filter. However, the use of a parallel capacitor comes with shortcomings such as high capacitance current and high inrush currents at fundamental frequency [20], [21].

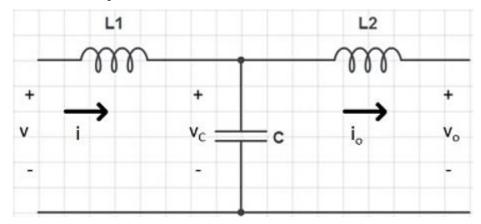

#### 2.4.2. LCL filter

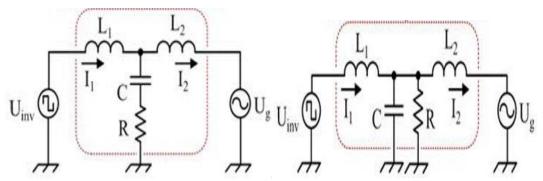

Figure 2.7 shows a typical circuit diagram of an LCL-filter which has two series inductors ( $L_1$  and  $L_2$ ) and a shunt capacitor(C) with  $V_{in}$  being the inverter side while  $V_{out}$  is the load side and it

should be noted that for three-phase systems, figure 2.7 is considered as a per-phase equivalent representation of a three-phase LCL-filter.

Figure 2.7: An LCL filter [20]

LCL filters overcome most of the issues related to L and LC-filters (first and second-order filters). LCL filters have notable merits over the second-order filters. Using LCL filters in a range of up to hundreds of kilovolt-amperes (kVA) provides excellent results however at relatively small values of inductor and capacitor hence reducing the filter overall costs. LCL filters give improved decoupling between grid and filter, as compare with first and second-order filters in case of grid-tie inverters. LCL-filters have a steep attenuation of -60dB/decade to switching frequency in bode as opposed to the first and second-order filters with -20dB/decade and -40dB/decade respectively [20], [22].

However, LCL filters oscillations may stay permanently and possibly damage the whole system due to a resonant condition. Around the resonant frequency, instability in current and voltage can be introduced due to resonance. To mitigate this effect, a damping resistor is added to an LCL-filter circuit [20]. By adding this damper, the damping and attenuation reduces [21]. 2.7 is a transfer function of the LCL filter and figure 2.7 and 2.8 show LCL filters with a series and parallel damping resistor incorporated, respectively. Series damping resistor results to a larger equivalent impedance of R and C as opposed to the parallel damping resistor. Therefore; high-frequency harmonics current flowing through C is bigger in series damped compared to a parallel damped filter. Hence; a series damped LCL-filter has a better effect on suppressing high-frequency harmonics [20], [21], [22].

Figure 2.8: With series damping resistor [21]

Figure 2.9: With parallel damping resistor [21]

The design of an LCL-filter can be achieved using 2.7 to 2.11.  $Z_B$ ,  $C_B$ ,  $V_{\phi}$  and P are a base impedance, base capacitance, inverter output phase voltage as well as the inverter rated power respectively. The calculated values are the same for all three phases in a three-phase system [20], [21], [22].

$$Z_B = \frac{V_{(\varphi)}}{P}$$

$$C_B = \frac{1}{\omega Z_B}$$

$$C_1 = \frac{0.01}{0.05} \times C_B$$

$$L_{1} = \frac{V_{IN}}{6 \times f_{SW} \times \Delta I_{max}} \text{ where } \Delta I_{max} = 0.1 I_{max}$$

$$L_2 = \frac{\sqrt{\frac{1}{k_a^2} - 1}}{C_1 \times \omega_{sw}^2}$$

(where  $k_a$  is an attenuation factor of 20%)

## 2.5. The PWM control techniques

The PWM control technique, in the context of three-phase inverters, can be defined as a method of generating appropriate PWM signal for switching the switching devices of a universal bridge such that a desired AC waveform is obtained at the output terminals of a ZSI [1], [18], [23]. Since the ZSI was proposed in 2003, lots of work has been done in this subject, especially on PWM control methods [9]. Three most common PWM control strategies in literature are discussed in this paper; viz. a simple boost control (SBC), constant boost control (CBC) and maximum Boost Control (MBC) techniques [1], [3], [6], [7], [9], [12], [13] [18], [23].

#### 2.5.1. Simple Boost Control

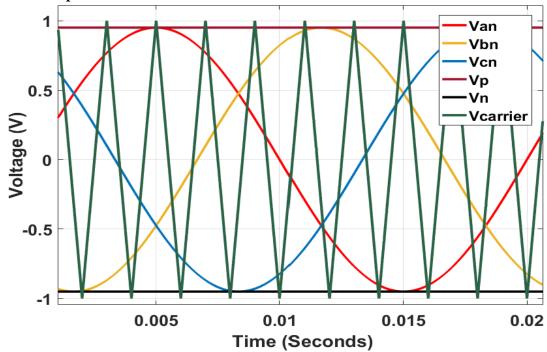

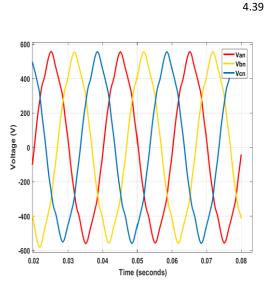

Figure 2.9: Simple boost control waveforms

Figure 2.10 shows a signal diagram of an SBC technique. A simple boost control uses two straight lines ( $V_p$  and  $V_n$ ), a set of three-phase reference voltages ( $V_{an}$ ,  $V_{bn}$  and  $V_{cn}$ ) and the triangular carrier wave ( $V_{carrier}$ ). A carrier wave is either equal to, greater than or less than the two straight lines ( $V_p$  and  $V_n$ ). When a carrier wave is greater than  $V_p$  or less than  $V_n$ , a ZSI is operating in a shoot-through state (mode 3) else; it is operating at in either an active or zero state (mode 1 and mode 2).

When a triangular waveform is greater than an upper straight line or lower than a bottom straight line; a ZSI operates in a shoot-through state. Otherwise, a ZSI operates like a VSI and SBC technique operates like sine-PWM (SPWM) technique which is a traditional control technique used to control VSIs. This method is the simplest; however, the resulting voltage stress across the switching devices is relatively high because some traditional zero states are not utilized. Output voltage for SBC technique is given by 2.12 below [5], [10], [12], [18], [23]:

$$V_{ABC(\varphi)} = \sqrt{3} \, m_{SBC} B_{SBC} \frac{V_{in}}{2}$$

(where m<sub>SBC</sub> and B<sub>SBC</sub> are modulation index and boost factor for SBC technique respectively)

#### 2.5.2. Constant Boost Control

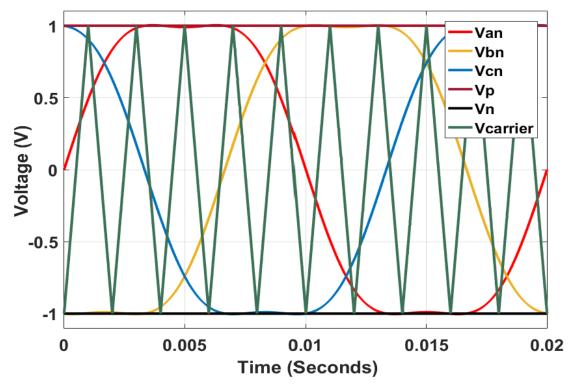

Figure 0.1: Constant boost control waveforms

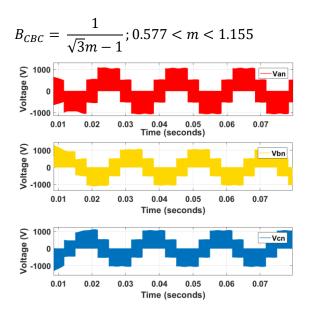

Figure 2.11 shows a signal diagram of a CBC technique. A constant boost control also uses two straight lines ( $V_p$  and  $V_n$ ), a set of three-phase reference voltages ( $V_{an}$ ,  $V_{bn}$  and  $V_{cn}$ ) injected with a third harmonic signal and the triangular carrier wave ( $V_{carrier}$ ). A carrier wave is either equal to, greater than or less than the two straight lines ( $V_p$  and  $V_n$ ). When a carrier wave is greater than  $V_p$  or less than  $V_n$ , a ZSI is operating in a shoot-through state (mode 3) else; it is operating at in either an active or zero state (mode 1 and mode 2) [10], [12], [18].

Constant boost control reduces the volume and cost of the design components, by keeping a shoot-through duty ratio constant. At the same time, a greater voltage boost for any given modulation index is desired and the reduced voltage stress across the switches is possible with Constant Boost Control. A constant boost control achieves the greater voltage gain (over SBC) while always keeping the shoot-through and hence duty ratio constant. Figure 15 shows the sketch map of the maximum constant boost control with third harmonic injection. Output voltage for CBC technique is given by 2.13 below [10], [12], [18]:

$$V_{ABC(\varphi)} = \sqrt{3} m_{CBC} B_{CBC} \frac{V_{in}}{2}$$

2.13

where  $m_{CBC}$  and  $B_{CBC}$  are modulation index and boost factor for CBC technique respectively.

#### 2.5.3. Maximum Boost Control

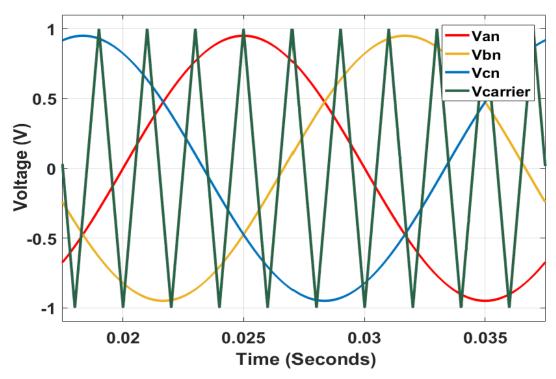

Figure 0.2: Maximum boost control waveforms

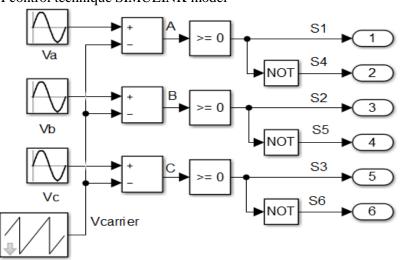

Figure 2.12 shows a signal diagram of a MBC technique. A maximum boost control uses two a set of three-phase reference voltages ( $V_{an}$ ,  $V_{bn}$  and  $V_{cn}$ ) and the triangular carrier wave ( $V_{carrier}$ ) only. A carrier wave is either equal to, greater than or less than the peak value s (positive and negative peak) of a three-phase reference signals. When a carrier wave is greater than positive peaks or less than negative peaks of a three-phase reference signal, a ZSI is operating in a shoot-through state (mode 3) else; it is operating at in either an active or zero state (mode 1 and mode 2) [5], [10], [12], [18], [23].

This strategy achieves a reduction in the voltage stress across the switching devices under the desired voltage gain. This is very important for the efficient control of the ZSI. The maximum boost control does this by turns all traditional zero states into a shoot-through state [11]. It is implemented in a very similar manner to simple boost control except that the two constant enveloping lines are not included. The third harmonic injection can also be used to extend the modulation index range. Turning all zero states into shoot-through states can minimize the voltage stress. However, this method introduces a low-frequency current ripple that is associated with the output frequency in the inductor current and the capacitor voltage. This will cause a higher requirement of the passive components when the output frequency becomes very low. Therefore, the maximum boost control is suitable for applications that have a fixed or relatively high output frequency. Output voltage for CBC technique is given by 2.14 below [10], [12], [18]:

$$V_{ABC(\varphi)} = \sqrt{3} m_{MBC} B_{MBC} \frac{V_{in}}{2}$$

2.14

(where m<sub>MBC</sub> and B<sub>MBC</sub> are modulation index and boost factor for CBC technique respectively)

#### 2.6. Conclusion

This chapter compared three-phase ZSIs to three-phase VSIs and CSIs in terms of performance and reliability. The basic design principles of a three-phase ZSI, LCL-filter and PWM control techniques were then underlined. Their basic principles form the basis for the development of chapter 4. Chapter 3 discusses a methodological approach that was used to achieve the objectives of this research study.

# 3. METHODOLOGY

This chapter outline the methodological approach that was used in this research study to fulfil the aims and objectives discussed of the research study outlined in chapter 1. As discussed earlier in chapter 1, the purpose of this research study is to investigate the performance response of a Z-source inverter when different PWM control techniques are applied to it while varying the input variables and; use the gained knowledge from the aforementioned study to develop a different inverter topology with an improved performance relative to a classical Z-source inverter.

A systematic approach that was employed to achieve the above mentioned objective involved the following series of steps:

- Review of literature

- Design of a three-phase Z-source inverter and a PWM control techniques

- Selection of a software tool on which implement a ZSI and a CB-ZSI

- Collection and analysis of results of a ZSI

- Development of a performance criteria of a CB-ZSI

- Design of a three-phase CB-ZSI

- Collection and analysis of results of a CB-ZSI

- Conclusion

#### 3.1. Literature review

Literature review focused on the background theory and design principles of Z-source inverters, three-phase filters and PWM control techniques. ZSIs were compared to traditional topologies of inverters (VSI and CSI), in terms of operational inherent reliability and the output power quality. Particular attention was paid to different applications currently in the industry and future directions of ZSIs thus, motivating a necessity of this dissertation.

The in-depth study of the operation of a classical three-phase Z-source inverter was done. This involved the equivalent circuit analysis of a Z-source inverter across its three possible operating states viz. the active, zero and shoot-through states. This analysis resulted in a primary equation of a boost factor (2.6) which holds across all three PWM techniques.

Three most common PWM control techniques in literature viz. simple boost, constant boost and maximum boost control technique; were studies [1], [3], [6], [7], [9], [12], [13] [18], [23]. Parameters such as a boost factor (B), gain factor (G), voltage stress across switching devices (V<sub>stress</sub>) and percentage of total harmonics distortion (%THD) were compared across all three PWM techniques and the interdependent relationships between these parameters for the same PWM control technique were also studied.

Boolean algebra was also studied. The study focused on the formulation and interpretation of truth tables which is a tool that was used to span a complete switching behaviour of each of the three PWM techniques. The methods of formulating Boolean functions from a truth table were also investigated during a literature survey which was found to be divided into two methods viz. sum-of-product (SOP) and product-of-sum (POS) methods [24]. The methods optimizing Boolean functions formulated using SOP and/or POS methods were also part of a literature survey which incorporated the use of Boolean algebra identities and the use of karnaurgh maps (k-maps) [24].

#### 3.2. Design of a three-phase Z-source inverter circuit

The design of a ZSI circuit was as per the following specifications; input DC voltage ranging from 200 V to 500 V, switching frequency at 10.05 kHz and a total power rating of 2000 W. An input range of 200V-500V was selected for this research study in alignment to reference publications that were consulted in a literature survey whose input voltages in their studies fall in between this range, therefore; results of this research study can directly be compared to those of reference publications.

Furthermore, a range of 200-500V simulates a real situation of renewable energy sources that have low characteristic DC-output voltages such as photovoltaic cells or arrays [25]. A switching

frequency of 10.05 kHz was selected using (4.2) which states that a normalized frequency ( $m_f$ ) should be an odd multiple of 3 to be able to use a single triangular carrier wave ( $f_{\Delta}$ ) across all three phases in PWM control techniques design. Furthermore; at normalized frequencies of more than 21, the output voltage of the ZSI is exclusively independent on the frequency and entirely dependent of  $m_f$  [6].

A power rating of 2000W is a relatively low power rating that was selected to cater for future consideration of possible implementing a practical prototype of a Z-source inverter (in chapter 4) and a Capacitor Boosted-Z-Source Inverter (in chapter 5). During implementation, a prototype of this power rating will be realizable without incurring excessive cost since low power rated components will be required. The circuit design of a ZSI had four main steps which are presented in a block diagram in figure 3.2.

Figure 3.1: Z-source inverter design block diagram

The inductor design was achieved via (4.1) to (4.3), capacitor design was achieved via (4.4) and (4.5), LCL-filter design is covered in chapter 2 and was achieved via (2.7) to (2.11) and the selection of switching devices and a power diode was achieved via (4.6) to (4.8). All these equations used in a ZSI circuit design were discovered in a literature survey and at this point after the design process presented by figure 3.2, a circuit diagram shown in figure 2.3 (connected to 2kW load via a three-phase LCL-filter) was completely designed.

## 3.3. Design of PWM control techniques

During a literature survey, three main PWM control techniques appeared most frequently with others being often based on these main threes. Hence, this research study implements these PWM control techniques which are the simple boost control (SBC), constant boost control (CBC) and maximum boost control (MBC) pulse modulation width (PWM) techniques[1], [3], [6], [7], [9], [12], [13] [18], [23].

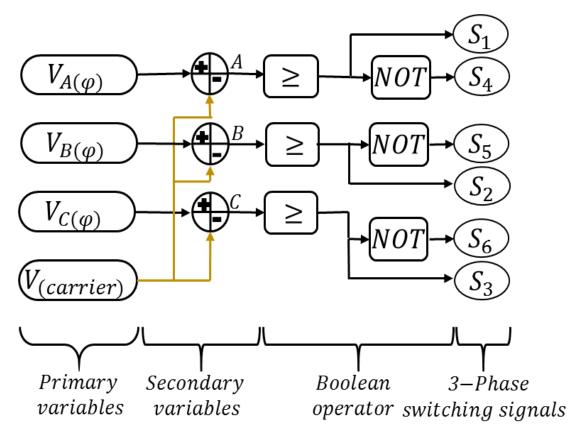

Figure 3.3 shows a general block diagram for a design of each of the three mentioned PWM control techniques.

Figure 3.2: PWM control technique design block diagram

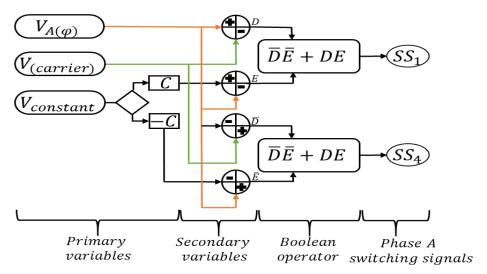

The first block of figure 3.3 involves mathematical definition of modulation signals for each of the three PWM control techniques. Those are a fundamental three-phase reference waveform  $(V_{ac(3\phi)})$  and a triangular carrier wave  $(V_{carrier})$  for a maximum boost PWM technique [7], [9], [12], [13]; a fundamental three-phase reference waveform, a triangular carrier waveform and two constant voltages  $(V_{constant})$  enveloping a fundamental reference waveform for simple boost PWM control technique [1], [3], [6], [12]; a third harmonic-injected fundamental three-phase reference waveform  $(V_{ac(3\phi, TH-Injected)})$ , a triangular carrier waveform and two constant voltages enveloping a fundamental reference waveform for a constant boost PWM technique [10], [12], [18], [23].

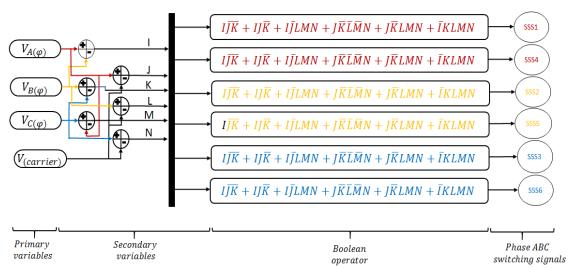

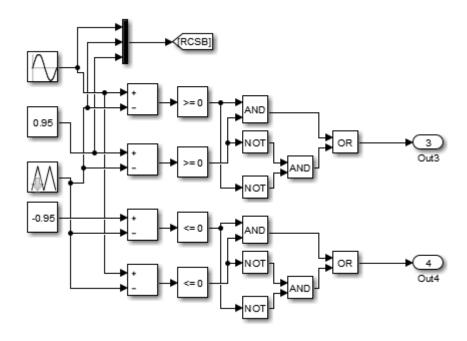

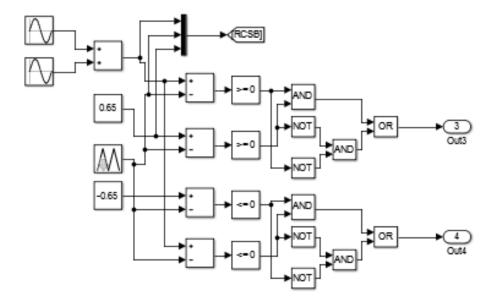

The second block formulate secondary variable which are functions of aforementioned modulating signals for each PWM control technique. These secondary variables are of Boolean type; that is, they are either 0 or 1 when a value less than or greater than zero is assigned to them, respectively. The main purpose of these secondary variables is tell relationships between all the modulating signals at any given time across a period of fundamental reference signals  $V_{ac(3\phi)}$  or  $V_{ac\ (3\phi,\ TH-Injected)}$ . That is, by looking at the states of secondary variable at any given instance; one can precisely tell the order of modulating signals  $(V_{a(\phi)},\ V_{b(\phi)},\ V_{c(\phi)},\ V_{a(\phi)-TH-Injected},\ V_{b(\phi)-TH-Injected},\ V_{constant})$  from the highest to the lowest at any particular time point. Refer to an example below based on row 28 of table 4.9 in chapter 4 and figure 3.4 for a graphical interpretation of information presented by the secondary variables.

## IJKLMN = 001000 mean:

- $\bullet \qquad \quad V_{a(\phi)} \ is \ less \ than \ V_{b(\phi)}$

- $\bullet \qquad V_{b(\phi)} \ is \ less \ than \ V_{c(\phi)}$

- $\bullet \qquad V_{c(\phi)} \text{ is greater than } V_{a(\phi)}$

- $V_{a(\phi)}$  is less than  $V_{carrier}$

- $\bullet \qquad V_{b(\phi)} \ is \ less \ than \ V_{carrier}$

- $V_{c(\phi)}$  is less than  $V_{carrier}$

$$\therefore V_{a(\varphi)} < V_{b(\varphi)} < V_{c(\varphi)} \text{ and } V_{carrier} > V_{c(\varphi)} > V_{b(\varphi)} > V_{a(\varphi)}$$

Figure 3.3: MBC modulating signals showing case 8 in table 4.9 [14]

Figure 3.4 shows state where secondary variables IJKLMN are having a Boolean value of 001000. This is a shoot-through state by definition and the switching devices of a highest phase signal,  $V_{c(\phi)}$ , are gated-on simultaneously (for a duration for which IJKLMN = 001000 holds). As evident in figure 3.4,  $T_5$  (which represents  $SSS_2$  table 4.9) and  $T_2$  (which represents  $SSS_5$  table 4.9) are gated on for this duration. It should be noted that the states of secondary variable change many more times in one period (T) subject to frequency of a triangular carrier wave in a simulation or physical prototype, figure 3.4 shows a low frequency triangular carrier for explanatory purposes.

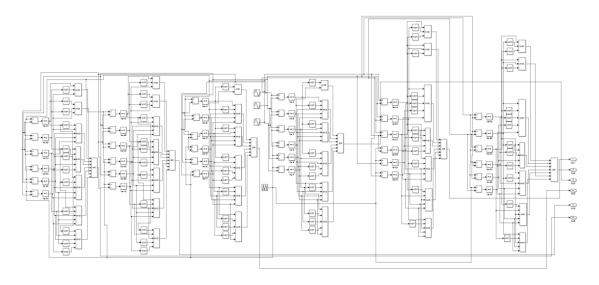

Therefore; secondary variables formulated across PWM control techniques (D, E, F, G, H for SBC and I, J, K, L, M, N for MBC PWM technique) pinpoint the active states (mode 1 of operation in chapter 2), zero states (mode 2 of operation in chapter 2) and shoot-through states (mode 3 of operation in chapter 2). This information is then used to create truth-tables that define switching behaviours of PWM control circuits for all possible states of secondary variables for each PWM technique. SOP method that was used to derive Boolean equations that describe switching behaviours of PWM control circuits. Kanaurgh maps (k-maps) were used to optimise Boolean equations for PWM control circuits before they were implemented on a simulation tool. Figure 3.4 shows a k-map for optimising MBC PWM technique Boolean functions SSS<sub>1</sub> – SSS<sub>6</sub>.

Figure 3.4: K-map for optimising Boolean equations SSS1 – SSS6

Figure 3.4 shows a k-map for a Boolean equation with 6 variables (I, J, K, L, M and N in the case of MBC PWM technique presented in this research study). Equations  $SSS_1 - SSS_6$  had up to 24 terms in their raw form and were optimised to up to 8 terms thanks to the k-map optimisation method.

#### 3.4. Selection of a simulation tool

After a paper design of a Z-source inverter and PWM control techniques was complete, it was crucial to select a suitable software tool in which to implement the designed ZSI and PWM control techniques.

Two software packages were under consideration, viz. power system computer aided design (PSCAD) and Matlab. The suitability of software was influenced by the ease of usability, analysis of percentage of harmonics distortion capability as well as the flexibility in displaying results such that the graphical results can be exported to editor window to edit them to improve the imagine quality of figures in the dissertation.

Both PSCAD and Matlab have capabilities of modelling a ZSI and the PWM control circuits and they both features a Fast-Fourier transform (FFT) based methods of analysing the percentage of total harmonics distortion [19]. However, PSCAD had the following limitations: It only supports plots in time domain and cannot plot harmonic magnitude or phase versus frequency and graphical results cannot be exported as picture files [19]. These limitations undermine the

collection of results for a purpose of reporting in dissertation while Matlab on the other hand; takes advantage of PSCAD's limitations and turns them into its strength with regards to appropriateness to this research study. Apart from the above stated facts, literature has shown bias towards Matlab over any other possible software in implementation of inverter related projects.

Hence, Matlab was a selected software package used to model all Z-source inverter and PWM control circuits for this research study.

#### 3.5. Results of a ZSI and discussion

After a ZSI and PWM control techniques were successfully implemented in Matlab results were taken from the simulation. A sample table shown below was used to collect data from a simulated ZSI prototype for each of the three PWM control techniques.

Table 3.1 Sample table for collecting results

|   | Varying input voltage and modulation index |          |          |          |          |          |          |          |          |          |          |          |          |          |          |          |              |

|---|--------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--------------|

| 1 | m                                          | 0.6<br>5 | 0.6<br>5 | 0.6<br>5 | 0.6<br>5 | 0.7<br>5 | 0.7<br>5 | 0.7<br>5 | 0.7<br>5 | 0.8<br>5 | 0.8<br>5 | 0.8<br>5 | 0.8<br>5 | 0.9<br>5 | 0.9<br>5 | 0.9<br>5 | 0.<br>9<br>5 |

| 2 | V <sub>IN</sub>                            | 200      | 300      | 400      | 500      | 200      | 300      | 400      | 500      | 200      | 300      | 400      | 500      | 200      | 300      | 400      | 5<br>0<br>0  |

| 3 | $V_{DClink}$                               | -        | -        | 1        | -        | -        | -        | -        | -        | -        | 1        | -        | -        | -        | -        | -        | -            |

| 4 | $V_{AC(3\phi)}$                            | -        | -        | ı        | -        | -        | -        | -        | -        | -        | ı        | -        | -        | -        | -        | ı        | -            |

| 5 | Stress<br>– ratio                          | -        | -        | 1        | -        | -        | 1        | -        | -        | -        | 1        | -        | -        | 1        | 1        | 1        | -            |

| 6 | В                                          | ı        | ı        | ı        | 1        | ı        | 1        | 1        | 1        | 1        | ı        | ı        | 1        | -        | 1        | 1        | -            |

| 7 | mB                                         | -        | -        | -        | -        | -        | -        | -        | -        | -        | 1        | -        | -        | -        | -        | -        | -            |

| 8 | %THD                                       | -        | -        | -        | -        | -        | -        | -        | -        | -        | -        | _        | -        | -        | -        | -        | -            |

Table 3.1 above is a tool that was used to collect results in this research study. The second column of this table feature the two main input variables, viz. the input voltage and a modulation index as well as six key performance parameters of a ZSI, viz. the DC-link voltage, output AC-voltage amplitude, voltage stress ratio across the switching devices, boost factor, gain factor as well as the percentage of total harmonics distortion.

As stated earlier in section 3.2; an input range of 200V-500V was selected because most input voltages of the reference publications for this research study fall in between this range therefore; results of this research study can directly be compared to those of reference publications. A modulation index range of 0.65 - 0.95 was carefully selected such that all PWM control technique are defined in this range. SBC, CBC and MBC PWM control techniques have different operating

ranges of a modulation index and therefore, a common range for all three PWM control techniques had to be selected. Furthermore, the range of 0.65 - 0.95 if far away from the asymptotes defined by (4.24), (4.26) and (4.39) of SBC, CBC and MBC PWM control techniques respectively and hence all three PWM control techniques are at stable operating state in modulation index in this range.

Therefore, the collection of data included the population of table 3.1 for each PWM control technique and graphical results were displayed for one case in a table. This case was chosen to be column 3; the third column where the input voltage is 200V at a modulation index of 0.65.

The analysis of results involved graphically presenting the relationships and trends discovered after populating table 3.1 for all three PWM control techniques. The relationships presented were; output voltage amplitude vs input DC-voltage (at a constant modulation index of 0.65), output voltage amplitude vs modulation index (at a constant input voltage of 200V), DC-link voltage vs input DC-voltage (at a constant modulation index of 0.65), DC-link voltage vs modulation index (at a constant input voltage of 200V), voltage stress across switching devices vs modulation index and the percentage of total harmonics distortion vs modulation index.

Relationships between these key performance parameters were recognised and classified as linear of nonlinear, increasing or decreasing relationships and the rate of change (gradient) was also noted. To confirm validity of a simulation of a ZSI and a PWM control technique (for all three PWM control techniques), a random column was chosen from table 3.1 for which theoretical and practical key performance parameters were compared. This is achieved in table 4.6, 4.8 and 4.11 in chapter 4.

## 3.6. Development of a CB-Z-Source Inverter performance criteria

A Capacitor Boosted-Z-Source Inverter was simply going to be given merits based on showing improved readings on the key performance parameters as compared to those of a Z-source inverter for the same input conditions. That is; a larger DC-link voltage and hence the boost factor, a larger gain factor and hence the amplitude of an AC output voltage, a smaller voltage stress across the switching devices and less percentage of total harmonic distortion; in a CB-ZSI than in a ZSI when all three different PWM control techniques are applied at similar input conditions.

#### 3.7. Design of a CB-Z-Source Inverter